# 以溫控式校正系統評估 MOSFET 應力計特性 楊明奕¹ 鍾 賢¹\* 羅本喆¹ 趙永清² 曾崑福³

1 國防大學理工學院半導體實驗室 2 台灣積體電路製造股份有限公司 3 親民技術學院電子工程系

# 摘 要

相較於傳統之壓電阻微應力計,MOSFET 元件具有使用面積小的優點,故如能開發 MOSFET 微應力計取代壓電阻,將會大幅降低製程成本。基於此,本文主要在探討 MOSFET 應力計受應力影響的行為變化及開發與其相對應的量測技術,此新技術的優點在於能同時提供熱與機械應力負載的環境、能結合現有量測平台與技術、價格便宜且簡單易製等。經由自晶片設計起的一套完整實驗過程,本文結過顯示 MOSFET 元件受應力影響或溫度效應後的電流特性變化呈線性結果且標準差介於 7~23%,相較傳統壓電阻應力計 10%而言尚稱合理。利用溫控量測技術發現溫度變化1°C 相當於 7 MPa 的應力變化,顯見溫度效應對應力計影響極為重要。綜上所述,本文已成功驗證 MOSFET 元件具有作為應力計的潛力。

關鍵詞:MOSFET應力計,應力效應,溫控量測,四點彎曲治具

# **Characteristic Evaluation on MOSFET Stress Sensor Through the Temperature-Controlled Calibration System**

Ming-I Yang<sup>1</sup>, Hsien Chung<sup>1\*</sup>, Ben-Je Lwo<sup>1</sup>, Yung-Ching Chao<sup>2</sup> and Kun-Fu Tseng<sup>3</sup>

<sup>1</sup>Semiconductor Laboratory, Chung-Cheng Institute of Technology, National Defense University

<sup>2</sup>Backend Technology and Service Division, Taiwan Semiconductor Manufacturing Company

<sup>3</sup>Department of Electronic Engineering, Chin-Min Institute of Technology

#### **ABSTRACT**

Comparing with the traditional piezoresistve stress sensors, the extremely small MOSFET devices bring more flexible chip circuit design and much cheaper sensor costs. To this end, the main purpose of this paper is to evaluate the characteristics of MOSFET stress sensors and to develop the related measurement methodology, which takes the advantages of simple, cheap, compatible with the probe station and related measurement technology, and able to apply thermal and mechanical loads simultaneously. With the newly developed technology, the mechanical, thermal, and thermo-mechanical MOSFET behaviors were measured, and linear relationship were obtained. Compared with 10% of variations for the piezoresistive sensors under stress loading, the 7 to 23% of variations for the p-MOSFET sensors show similar sensitivities. Furthermore, the temperature effect was found extremely important for MOSFET since 1°C of temperature rise produce the same effect as 7 MPa of stress loading. Consequently, it is concluded that the MOSFET devices has a great potential to be the stress sensors.

Keywords: MOSFET stress sensor, mechanical effects, thermal effects, 4PB fixture

文稿收件日期 97.7.29; 文稿修正後接受日期 98.5.5;\*通訊作者 Manuscript received July 29, 2008; revised May 5, 2009;\* Corresponding author

## 一、前 言

積體電路(Integrated Circuit)晶片朝向縮小化與高密度電路設計的趨勢眾所皆知,源自構裝過程中伴隨的應力大小亦會隨之在運能已上,因元件密度集中使得晶片在運作時產生的廢熱問題、晶片與構裝材料間熱態展係數的差異導致材料間產生熱應力、構裝過產生數應力、構裝過程性壓縮應力、不同構裝材料本身吸濕膨脹能力等,均可能導致層量生之吸濕膨脹應力等,均可能導致層量生之吸濕膨脹應力等,均可能學性上嚴重人。因此,研究可有效監控電子構裝有不容忽視。因此,研究可有效監控電子構裝有不容忽視。因此,研究可有效監控電子構裝有不容忽視。因此,研究可有效監控電子構裝有不容忽視。因此,研究可有效監控電子構裝有不容。因此,研究可有效監控電子構裝有不容。因此,研究可有效監控電子構裝有不容。

為了監控且在不破壞構裝結構條件下偵 測晶片承受應力變化的情形,早期學者研究集 中在以矽為基底之壓電阻效應(Piezoresistive effect) 特性,藉由佈值(Implant)與擴散 (Diffusion) 等製程技術將壓電阻應力計 (Piezoresistive Stress Sensors)以片電阻(Sheet Resistance)之型式製作於晶片上,再將測試晶 片予以構裝。因此,構裝後經由元件之訊號傳 輸即可實地(In-Situ)量測構裝內晶片上的應力 變化行為。又先前的研究證實應力對壓電阻元 件電阻具有線性變化的趨勢[3],其原理是當 應力施加在原本對稱的晶體結構時,將使其喪 失原本的對稱性而導致電阻率的改變,所以藉 由量測元件的電性並配合相關理論及校正 (Calibration)數據即可推知晶片於構裝內所產 生之應力[4]。惟透過一般製程僅能製作小阻 值的片電阻,若要將阻值加大至適當量測範圍 須將元件以串連繞線成薔薇狀(Rosette)的方 式製作,故會佔據較大的面積(約 100×100 μm²),在現今強調輕、薄、短、小的製成趨勢 而言已不符需求。

既然應力可造成被動元件 (Positive Devices)如壓電阻的特性改變,在現今半導體技術中金氧半場效電晶體 (Metal-Oxide-Semiconductor Field Effective Transistor, MOSFET)亦是以矽為基底製造運用的主動元件(Active Devices),因此於1980年代開始許多學者即積極研究以主動元件替代被動元件作為應力計的可行性,其中尤以研究應力與應變是否會造成 MOSFET 特性改變更為許多學者在元件效能提昇的範疇下被廣泛討論[5-6]。基於此,2000年 Jaeger 等提出

以互補式金氧半場效電晶體(Complimentary Metal Oxide Semiconductor Field Effective Transistor, CMOS)應力計即為嘗試以主動元 件監測應力改變之可行性[7]。如此除可避免 如壓電阻般需多次量測的困擾外,並且 CMOS 應力計所耗費的空間(約5 μm²)遠小於傳統壓 電阻應力計(約 10000 um²),對於未來朝向高 元件密度設計後的晶片應力監控需求而言,無 疑更是大幅降低單位面積所耗費的成本。文獻 中亦有學者利用四點彎曲(Four Point Bending) 治具在 MOSFET 上施加應力,其結果顯示 MOSFET 電性隨施加之應力方向不同而變 化,且在不同佈局方向之元件也有效能上的差 異[8]。探究上述研究之物理機制,是因為應 力會改變半導體材料帶電載子(Cattier)的有效 質量(Effective Mass)與載子散射(Scattering), 並造成半導體材料的能帶(Energy Band)發生 改變[9-11],使得元件載子漂移率(Mobility)產 生變異。由於理想電晶體汲極電流(Drain Current)與載子漂移率成正比,所以藉由量測 MOSFET 汲極電流的變化情形即可直接量測 出元件受到應力的大小。

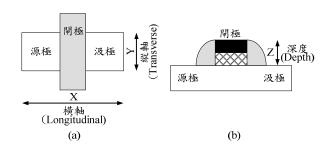

在應力對於不同型式之 MOSFET 元件 (n-MOSFET 與 p-MOSFET)造成載子漂移率的 改變方面亦有學者探討。2005 年 Chan 等人針 對應力施加於 MOSFET 元件的方向不同所引 致的特性變化大致做個整理,該研究指出若 MOSFET 元件之縱軸、橫軸等方向定義如圖 1,則載子漂移率變化情形會如表 1 的方式呈 現[12]。惟文獻大多朝向以製程引致應力使元 件效能提昇,對於應用 MOSFET 元件於即時 監控的應力感測計而言卻寥寥可數,亦未討論 當環境溫度改變所會造成 MOSFET 的電性影 響。因此,本文除將探討以 MOSFET 元件作 為應力計之可行性外,並將研發簡單價廉的量 測機制以嘗試施予不同應力與溫度環境,甚至 二者耦合發生時均能夠量測 MOSFET 元件的 電性變化情形,且將量測結果以量化方式呈 現。最後,本文將評估 MOSFET 元件作為應 力感測計之可行性,期將結果提供未來應用於 電子構裝業者的參考依據。

圖 1. MOSFET 方向定義示意圖,其中(a)俯視圖; (b)側視圖。

表 1. 單軸應力方向型式引致 MOSFET 載子漂移率 提昇對照表[12]

| ************************************** |          |          |

|----------------------------------------|----------|----------|

| 方向                                     | n-MOSFET | p-MOSFET |

| 横軸(X)                                  | 伸張       | 壓縮       |

| 縱軸(Y)                                  | 伸張       | 伸張       |

| 深度(Z)                                  | 壓縮       | 伸張       |

# 二、實驗步驟

不論是 n-MOSFET 及 p-MOSFET 元件, 文獻的討論均指出製程引致應力能提昇元件 效能[5,11-15]。此外,文獻中亦指出 MOSFET 元件受應力後會增加飽和電流 (Saturation Drive Current, I<sub>D</sub>)藉以提昇效能,並且降低漏 電流(Leakage Current)、減少能耗[16-18]。然 而因文獻中指出 p-MOSFET 元件在受應力後 之效能提昇率優於 n-MOSFET 元件,且應力 可導致電洞(Hole)漂移率(Mobility)之增加率 大於電子(Electronic)漂移率四倍[14-15],顯見 p-MOSFET 元件在受應力後之相對靈敏度 (Sensitive)較 n-MOSFET 元件來得好。因此, 本文所探討應力和溫度效應對於 MOSFET 元 件電性的影響等等均選用 p-MOSFET 元件作 為測試樣本。

圖 2 是本實驗之流程圖,其中測試元件是由台灣積體電路製造股份有限公司(TSMC)利用 90 奈米標準製程所製造,MOSFET 元件通道長度(Channel Length)為 0.15 μm、通道寬度(Channel Width)為 1 μm,並依通道方向將晶圓(Wafer)分別以平行於通道方向的橫軸形式(Longitudinal, X 軸)及垂直於通道方向的縱軸形式(Transverse, Y 軸)切割成晶條(Strip)狀測試樣本,相關軸向定義示意圖詳如前述圖 1。接著實驗流程為在對晶條施以不同應力和溫

度的條件下量測元件「汲極電流 $(I_D)$ —汲極電壓 $(V_D)$ 」關係,期望從數據中探討應力效應和溫度效應對元件的影響。

圖 2. 實驗流程圖。

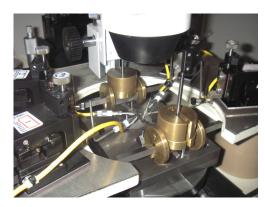

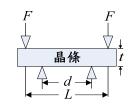

在圖 2 之機械應力(Mechanical Stress)量測方面,我們藉由本實驗室既有的四點彎曲 (Four-Point Bending, 4PB)治具(Fixture)架設晶條於探針量測平台上,此治具可藉由調整放置的砝碼而對晶條施加不同大小應力,元件特性則以下探針方式進行量測,實驗架設如圖 3 所示。圖 4 為四點彎曲法之示意圖,由簡單的材料力學公式推導可知[19]晶條中心位置表面所受的單軸(uniaxial)應力大小 $\sigma$ 為

$$\sigma = \frac{3F(L-d)}{t^2h} \tag{1}$$

其中F為砝碼所施加之力、t 及h 分別為晶條的厚度與寬度、L 為左右砝碼的間距、d 則為左右支點間的距離。由(1)式可知只要有效控制砝碼重量即可在晶條表面產生一固定單軸應力,並可藉由控制四點彎曲結構上砝碼及單點、施力點位置的不同而分別對晶條施以伸張 (Tensile)與壓縮(compressive)應力,即當L-d> 0時元件受伸張應力,反之當L-d< 0時元件將被壓縮。此外,部份學者也曾利用 ANSYS有限元素軟體模擬晶條在四點彎曲結構應分分佈情形,結果證實在支撐點內晶條表面受單軸應力且應力大小分佈均勻,因此可降低元件量測時因元件位置不同而會造成差異的疑慮 [20]。

圖 3. 實驗裝置架設示意圖。

圖 4. 四點彎曲法示意圖。

至於在溫度效應量測方面,因文獻尚無可量測應力又可同時提供恆溫環境的相關設備記載,所以需開發或修改現有四點彎曲治具使之變成可同時調整溫度與應力的量測環境,這部份細節將如下節所述。在實驗量測設備方面,本文針對 MOSFET 元件之「汲極電流( $I_D$ )—汲極電壓( $V_D$ )」特性量測均透過安捷倫科技(Agilent Technologies)製造型號為 4156C 之高精密度半導體參數分析儀(Precision Semiconductor Parameter Analyzer, Agilent 4156C)為之。

## 三、温控式校正系統之開發

到應力影響外,還會有高溫製程產生之溫度效

應。為了避免應力計使用時因溫度效應造成應

如前所述,在積體電路製程中元件除會受

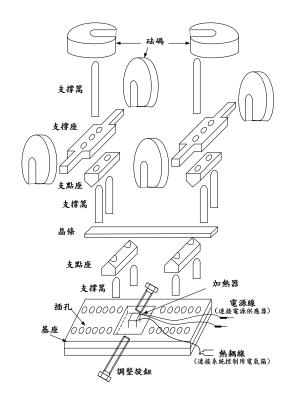

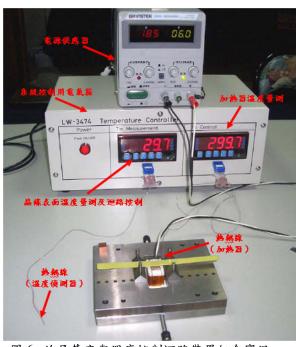

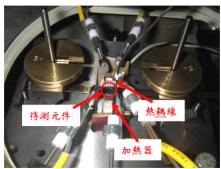

力量測誤差,探討溫度效應對元件的影響極為 重要。但能同時施加應力又能控制環境溫度的 簡單裝置則未見於文獻中,故研發改良「溫控 式校正系統 | 是本文重要的課題。此系統區分 二大部分:一是「四點彎曲校正治具改良」, 另一是「溫度控制迴路裝置設計」,分述如下: (一)在「四點彎曲校正治具改良」方面,由 於量測元件均位於晶條與治具中心附 近,因此本實驗室提出在四點彎曲校正 系統之基座中心挖洞並放置一個可調 整功率之加熱器的構想,如圖 5。圖 5 顯示加熱器包含二條連接線,分別是電 源線與熱耦線,其中電源線連接至電源 供應器並可設定輸出功率將加熱器加 熱以提高晶條溫度;熱耦線則接至系統 控制用電氣箱以測得加熱器實際溫 度,避免其因過熱而損壞。為了避免加 熱器直接碰觸晶條而產生額外的誤 差,吾人利用調整旋鈕以手動方式微調 加熱器與晶條間之距離,並確保加熱器 位在接近量測範圍的正下方以維持加 熱效能。

圖 5. 溫控式四點彎曲校正治具。

(二)在「溫度控制迴路裝置設計」方面,主 要是由系統控制用電氣箱及電源供應 器組合而成,整體架構則採用溫度迴路 控制方式製造恆溫環境,實驗裝置相片 如圖 6 所示。圖中系統控制用電氣箱上 含有二個溫度量測點,其中加熱器上之 熱耦線連接於右方的溫度量測儀表以 偵測其溫度;另一熱耦線則放置於晶條 中心表面附近偵測晶條實際溫度。在溫 度控制迴路裝置方面,則是先於系統控 制用電氣箱左方之晶條表面溫度量測 儀設定至欲量測之晶條溫度,然後打開 電源供應器並藉由控制迴路自動調整 提供於加熱器之功率以控制晶條溫 度。當位於晶條表面元件上的熱耦線偵 測溫度到達設定溫度範圍時,溫控迴路 隨即啟動或控制電源供應器輸出功率 以維持晶條恆溫效果。當溫度達到設定 範圍且保持穩定後,吾人即可量測該溫 度下之元件特性。

圖 6. 治具基座與溫度控制迴路裝置組合實況。

本實驗研發改良之「溫控式校正系統」可 與現行量測平台與技術相互結合,架設好後不 必移動量測相關設備,直接施加砝碼即可提供 應力負載環境;至於恆溫環境製造僅需加裝溫 度控制迴路系統即可提供。因此,本校正系統 的優點包括製造成本低廉,且製作及組裝非常 簡單,且能提供同時施加熱與應力負載的量測 環境。

# 四、實驗結果與討論

#### 4.1 機械應力量測分析

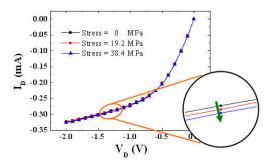

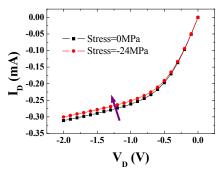

欲觀察 MOSFET 元件受應力的電性變化 情形,必須先從未受應力影響的條件下量測元 件「汲極電流 $(I_D)$ —汲極電壓 $(V_D)$ 」初始特性 方能做後續分析,亦即將爾後量得之受應力特 性曲線與此處之初始特性比較。圖 7 是對 p-MOSFET 元件縱軸施加伸張應力後的 I<sub>D</sub>-V<sub>D</sub> 變化情形,由圖中可發現應力確實對於 ID-VD 特性曲線造成影響。由於執行 p-MOSFET 元 件量測時必須操作在負偏壓的區域,本實驗直 接設定閘極電壓(V<sub>G</sub>)為-1.2V。另由於短通道 效應(Short-Channel Effect)使 In 在飽和區域 (Saturation Region)時仍會隨 VD 變化而持續增 加。此外,圖 7 元件係受到縱軸伸張應力影 響,所以飽和汲極電流(Saturation Drain Current, I<sub>Dsat</sub>)曲線朝增量方向改變,此現象與 表 1 中當 p-MOSFET 元件在縱軸施加伸張應

力時會提昇其漂移率的趨勢相符。

圖 7. 對 p-MOSFET 元件縱軸施加拉伸應力前後  $I_D$ - $V_D$  變化情形( $V_G$ =-1.2V)。

#### 4.1.1 飽和汲極電流(Ipsat)受應力的影響

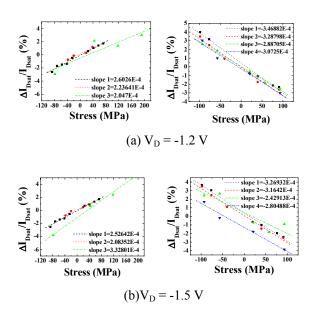

MOSFET 元件在電路設計上必須操作在 飽和區才能提供最佳的運作條件,因此必須選 定位於飽和區域的VD為條件分析ID受應力之 變化情形,圖8即每次量測結果ID分別在VD 為-1.2V、-1.5V 與-2.0V 時之特定點作分析比 較,其中左圖為對 p-MOSFET 元件縱軸施加 應力的結果;右圖則為對橫軸施加應力的結 果。圖8中各圖結果係以受應力後之飽和電流 相對變化量對應應力大小顯示,並經由線性擬 合(Linear Fitting)方式標示各線斜率(Slope)於 圖中,其中伸張應力為正值、壓縮應力為負 值, I<sub>Dsat</sub> 相對變化量增加為正值、減少為負值, 並以百分比表示。因應力感測計必須對應力影 響具有線性變化的特性始有開發價值,故本文 則對量測數據相對於應力變化均以線性擬合 方式表示,旨在探討 MOSFET 元件作為應力 計之可行性評估。

圖 8. 對 p-MOSFET 元件縱軸(左)與橫軸(右)施加 應力後 I<sub>D</sub>變化情形。

由圖 8 之結果可知對 p-MOSFET 元件縱 軸施加伸張應力時 ID 會隨之增加,反之則減 少,但對元件橫軸施加壓縮應力時In反而會 隨之增加,這些均符合表1不同軸向應力形式 會提昇元件載子漂移率的趨勢。表 2 則是將圖 8之量測結果綜整並做簡單的統計處理所得到 在不同 Vn 情況下 In 相對變化量之平均斜率, 表中顯示對縱軸與橫軸施加應力的斜率確有 不同趨勢,但以絕對值處理後則差異並不大。 觀察表 2 亦發現在不同 Vp 情況下的斜率相差 不大,表示元件只要在飽和區域上操作,則在 量測數據上並無太大差別。表2數據又顯示若 ID為 1 mA 時,當進入飽和區域時對縱軸施加 應力每增加 1MPa 會增加約 2.4×10<sup>-4</sup> mA 的電 流變化量;對橫軸施加應力每增加 1MPa 則會 減少約 3.0×10<sup>-4</sup> mA 的電流變化量。

表 2. 將圖 8 量測結果分析 I<sub>D</sub> 與應力之斜率關係 (單位:nnm/MPa)

| 斜率            | 縦軸           | 横軸            |

|---------------|--------------|---------------|

| $V_D = -1.2V$ | 229.53±28.24 | -317.90±25.33 |

| $V_D = -1.5V$ | 264.59±63.08 | -291.69±38.12 |

| $V_D = -2.0V$ | 230.63±35.85 | -285.84±28.41 |

#### 4.1.2 p-MOSFET 元件與壓電係數萃取

傳統壓電阻應力計均以受應力後電阻變化量來執行特性分析。依據歐姆定律(Ohm's Law)電流與電阻成反比關係,本文若能轉換電流變化量為電阻變化量,則亦可探討電阻變化與應力之關係。然而在探討 MOSFET 元件電阻模型方面,學者 Wu 等人於 2007 年提出MOSFET 元件總電阻( $R_{Total}$ )為通道電阻( $R_{CH}$ )與源極/汲極(S/D)電阻( $R_{SD}$ )組合的模型,最後利用  $R_{SD}/R_{CH}$ 比率隨著通道長度增加而減少並小於 1 的關係可決定  $R_{Total}$  [21-22],但處理過

程頗為繁瑣。基於此,我們直接將量測結果簡 單假設均遵循歐姆定律,即

$$R_{\text{Total}} = \frac{V_{\text{D}}}{I_{\text{D}}}$$

(2)

也就是說總電阻值來自於汲極電壓除以汲極電流。圖 9 是依此方式套用圖 8 之量測結果轉換而成,由圖中可知因電阻與電流成反比,所以元件之電阻變化斜率與電流變化斜率趨勢相反。

圖 9. 對 p-MOSFET 元件縱軸(左)與橫軸(右)施加 單軸應力後相對電阻變化情形。

同樣地,表 3 是將圖 9 之電阻變化情形綜整並做簡單的統計處理及線性擬合所得到在不同  $V_D$ 情況下電阻變化量之平均斜率。與表 2 相同,表 3 之縱軸與橫軸數據有著不一樣的趨勢,但以絕對值處理後差異亦不大,且與文獻趨勢相似[12-13,21-22]。相較於本實驗室先前研究傳統壓電阻應力計在受力 100 Mpa 時之電阻變化率約為 1.5 %至 2 %的結果[1],此處選用的 p-MOSFET 元件受力 100 MPa 時亦約有 2 %的變化,顯見以 MOSFET 元件作為應力計時的靈敏度與壓電阻應力計相距不遠,因此以 MOSFET 元件作為應力計的應為可行。

表 3. 圖 9 元件受應力後電阻變化量與應力之斜率 關係(單位:ppm/MPa)

| 111           |               |               |

|---------------|---------------|---------------|

| 斜率            | 縱軸            | 横軸            |

| $V_D = -1.2V$ | -230.68±29.85 | 316.30±23.30  |

| $V_D = -1.5V$ | -264.44±61.19 | 291.14±37.12  |

| $V_D = -2.0V$ | -232.08±37.70 | -285.98±25.10 |

為評估本實驗數值的穩定性,表4則是將 表 3 不同 Vn 樣本所計算出各斜率之標準差 (Standard Deviation)除以平均斜率值並以百分 比(%)表示。由表 4 呈現結果得知以橫軸在 V<sub>D</sub>=-1.2V 時所量測數據的相對標準差最小約 為 7%, 而以縱軸在 V<sub>D</sub>=-1.5V 時展現出來的相 對標準差最大約為23%。相較於文獻研究傳統 壓電阻式應力計相對標準差約為 10%來說 [23], MOSFET 元件後應力後亦呈現了一致性 (Uniformity), 此結果對於開發 MOSFET 元件 作為應力計的參考非常重要。至於在量測技術 方面本文雖已成熟,但由於晶條在四點彎曲治 具上為懸空狀態,且元件面積小使得下探針方 式較為複雜,所以易造成量測相對標準差差異 較明顯,因此如何降低整體量測結果的誤差值 尚有待後續研究持續改進,但本實驗已達成初 步評估 MOSFET 元件作應力計的預期成效。

表 4. 元件受應力後壓電阻係數之相對標準差(單位:%)

| 相對標準差                    | 縦軸 | 横軸 |

|--------------------------|----|----|

| $V_{\rm D} = -1.2 \rm V$ | 13 | 7  |

| $V_{\rm D} = -1.5 \rm V$ | 23 | 13 |

| $V_{\rm D} = -2.0 \rm V$ | 16 | 9  |

#### 4.2 温度效應量測分析

本文的另一個重大議題在於如何升溫 量測 MOSFET 元件的特性以探討溫度效 應對元件性能的影響。圖 10 為使用本實驗 所研發含加熱器的四點彎曲治具架設於量 測平台的情形,其中雖然熱耦線在溫度量 測上所耗的電能非常小,但為避免熱耦線 本身接觸晶條表面造成非必要的影響,故 將此組熱耦線放置接近但不碰觸待測元件 的相對稱位置上,以正確獲得待測元件實 際溫度並不致影響實驗結果。

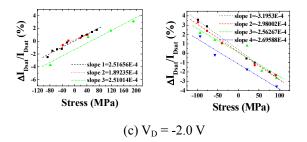

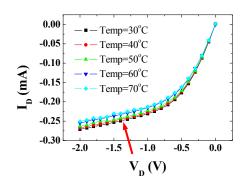

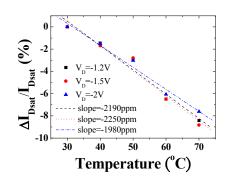

圖11為p-MOSFET元件於不同溫度條件量測所得到之  $I_D$ - $V_D$ 特性曲線,其結果顯示隨著溫度升高會造成飽和區  $I_D$  減少,探究其物理機制乃因 MOSFET 元件受溫度效應時,隨著溫度升高元件內載子散射機率變大故而導致漂移率變小,繼而造成  $I_{Dsat}$  降低成為此圖的情形。圖 12 則為選定不同  $V_D$  狀況下觀察  $I_{Dsat}$  變化量與溫度的關係,並使用線性擬合計算其斜率,由圖中可知受到溫度效應會對 MOSFET 元件造成負斜率之影響。

圖 10. 待測元件溫度效應架設圖。

圖 11. 溫度效應對 p-MOSFET 元件 I<sub>D</sub>-V<sub>D</sub> 關係圖。

圖 12. 溫度效應對 p-MOSFET 元件在不同  $V_D$  情况下之量測結果。

以温控式校正系統評估 MOSFET 應力計特性

為探討元件受溫度效應的影響相對於受機械應力影響的關係,此處選擇在室溫自然極度之結果(同樣為自斜率的元件)作比較,表 5 即為元件經圖 12 溫下在於應量測後所得的斜率與 4.1 節(室溫下在於樓軸施加伸張應力)量測得到的斜率之比較表。由表 5 可發現元件進入飽和區域後在下时表。由表 5 可發現元件進入飽和區域後在下間 VD 情況下量得之溫度與應力效應的斜率皆相差不大,表中亦顯示 p-MOSFET 元件在受溫度效應影響後 IDsat 變化的斜率與 4.1 節結果之比率差約為 7 倍數值,也就是說元件在溫度 吃1°C 時所受之影響相當於對其施以 7 MPa 的應力影響,因此溫度效應的影響對 MOSFET 元件應力計之開發極為重要,不容忽視。

表 5. 溫度效應(單位:ppm/°C)與橫軸施加機械應 力效應(單位:ppm/MPa)比較

| 斜率            | 溫度效應  | 横軸施加應力        |

|---------------|-------|---------------|

| $V_D = -1.2V$ | -2190 | -317.90±25.33 |

| $V_D = -1.5V$ | -2250 | -291.69±38.12 |

| $V_D = -2.0V$ | -1980 | -285.84±28.41 |

#### 4.3 温度效應與機械應力之耦合量測分析

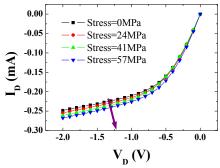

除了溫度效應量測外,本文之改良四點彎曲治具主要精神不但是能對元件施以應力來量測元件的特性,更希望能在應力施加的同時又能給予恆溫控制的環境以量測元件之耦合特性。圖 13 顯示在晶條表面溫度為  $50^{\circ}$ C 時對 p-MOSFET 元件縱軸施加伸張應力後之 $I_D$ - $V_D$  特性曲線,相較於 4.1 節室溫下伸張應力會提昇  $I_{Dsat}$  的相同趨勢,可見溫度升高並未影響元件受應力後特性曲線變化的趨勢。

圖 13. 50°C 時對 p-MOSFET 元件縱軸施加伸張應 力後之特性曲線。

依據先前的數據處理方式,我們同樣選定

表 6. 不同溫度對元件縱軸施加應力後 I<sub>Dsat</sub> 變化率 之斜率比較(單位:ppm/MPa)

| 斜率            | 50°C | 30°C         |

|---------------|------|--------------|

| $V_D = -1.2V$ | 1260 | 229.53±28.24 |

| $V_D = -1.5V$ | 1330 | 264.59±63.08 |

| $V_D = -2.0V$ | 1370 | 230.63±35.85 |

圖 14. 在 50°C 時對 p-MOSFET 元件縱軸施加壓縮 應力後之特性曲線。

# 五、結論

本文針對 MOSFET 元件作應力感測計的開發,結果顯示 MOSFET 元件不論在機械應力、溫度效應或耦合環境下的 I<sub>D</sub>-V<sub>D</sub>量測結果均可利用數據處理及線性擬合方式獲得電流變化量的斜率,其受應力影響後的特性趨勢並與文獻相符。另外,結果亦顯示 MOSFET 元件進入飽和區域後在不同 V<sub>D</sub>下受應力影響的程度無太大差異,此結果可提供未來電路設計上安插應力計的參考。又由於前述變化特性顯示線性關係,故 MOSFET 元件可作為應力感

測計之潛力。此外,本文之數據亦顯示本文對於量測治具的改良與開發有顯著的成效,此因本實驗設計之「溫控式校正系統」除能量測升溫時 MOSFET 元件特性變化外,亦能量測溫度與機械應力同時變化的裝置。由於利用上述裝置之量測結果顯示 p-MOSFET 元件溫度變化 1°C 相當於 7MPa 的應力變化量,所以溫度效應極為重要不能忽略。

綜上所述,本實驗結果經與壓電阻應力計比較可知 MOSFET 應力計除了面積小的優點外,其靈敏度與壓電阻相近。由於 MOSFET 元件為當前積體電路設計不可或缺的元件,故本文成果可提供未來 IC 設計時選擇欲放置應力量測元件的參考依據。

#### 致謝

感謝行政院國家科學委員會提供研究計畫(NSC 96-2221-E-606-024)支援研究所需經費。

# 參考文獻

- [1] Lwo, B. J., Chen, T. S., Kao, C. H., and Lin, Y. L., "In-Plane Packaging Stress Measurements Through Piezoresistive Sensors," Journal of Electronic Packaging Transaction of the ASME, Vol. 124, No. 2, pp. 115-121, 2002.

- [2] Lwo, B. J., and Lin, C. S., "Measurement of Moisture-Induced Packaging Stress With Piezoresistive Sensors," IEEE Transactions on Advanced Packaging, Vol. 30, Issue 3, pp. 393-401, August, 2007.

- [3] Lwo, B. J., Chen, Y. S., Chen, T. S., Li, J. M., Kao, C. H., Lin, C. Y., and Tseng, K. F., "Temperature Calibration on Piezoresistive Stress Sensors," Journal of Chung-Cheng Institute of Technology, Vol. 29, No. 1, pp. 15-21, 2000.

- [4] Lau, J. H., Thermal Stress and Strain in Microelectronics Packaging, Van Nostrand Reinhold Co., New York, U. S. A., Chap. 7, pp. 221-269, 1993.

- [5] Shimizu, A., Hachimine, K., Ohki, N., Ohta, H., Koguchi, M., Nonaka, Y., Sato, H., and Ostsuka, F., "Local Mechanical-Stress Control (LMC): A New Technique for CMOS-Performance Enhancement,"

- Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, pp. 19.4.1-19.4.4, Dec. 2001.

- [6] Murthy, A., Chau, R. S., Ghani, T., and Mistry, K. R., "Semiconductor Transistor Having A Stressed Channel," Intel Technology Journal, Santa Clara, CA, Patent No. US 6,885,084 B2, Intel, April. 26, 2005.

- [7] Jaeger, R. C., Suhling, J. C., Ramani, R., Bradley, A. T., and Xu, J., "CMOS Stress Sensors on (100) Silicon," IEEE Journal of Solid-State Circuits, Vol. 35, No. 1, pp. 85-95, Jan. 2000.

- [8] Chen, T. S., and Huang, Y. R., "Evaluation of MOS Devices as Mechanical Stress Sensors," IEEE Transactions on Components and Packaging Technologies, Vol. 25, No. 3, pp. 511-517, Sep. 2002.

- [9] Chun, S. K. and Wang, K. L., "Effective Mass and Mobility of Holes in Strained Si<sub>1-x</sub>Ge<sub>x</sub> Layers on (001) Si<sub>1-y</sub>Ge<sub>y</sub> Substrate," IEEE Transactions on Electron Devices, Vol. 39, No. 9, pp. 2153-2164, 1992.

- [10] Vogelsang, T. and Hofmann, K. K., "Electron Mobility and High-Field Drift Velocities in Strain Silicon on Silicon-Germanium Substrates," IEEE Transactions on Electron Devices, Vol. 39, No. 11, pp. 2641-2642, 1992.

- [11] Mohta, N. and Tompson, S. E., "Mobility Enhancement," IEEE Circuit and Device Magazine, Vol. 21, No. 2, pp. 18-23, Sep./Oct. 2005.

- [12] Chan, V., Rim, K., Ieong, M., Yang, S., Malik, R., Teh, Y. W., Yang, M., and Ouyang, Q., "Strain for CMOS Performance Improvement," Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, pp. 667-674, Sep. 2005.

- [13] Thompson, S. E., "Strained Si and the Future Direction of CMOS," Proceedings of the 9th International Database Engineering and Application Symposium, Concordia University, Montreal, Canada, July 2005.

- [14] Takagi, S. I., Hoyt, J. L., Welser, J. J., and Gibbons, J. F. "Comparative Study of Phonon-Limited Mobility of Two-Dimensional Electrons in Strained and Unstrained Si Metal-Oxide-Semiconductor

- Field-Effect Transistors," Applied Physics Letters, Vol. 80, No. 3., pp. 1567–1577, 1996.

- [15] Lundstrom, M., and Ren, Z., "Essential Physics of Carrier Transport in Nanoscale MOSFETs," IEEE Transactions on Electron Devices, Vol. 49, pp. 133-141, Jan. 2002.

- [16] Horstmann, M., Wei, A., Kammler, T., Hntschel, J., Bierstedt, H., Feudel, T., Frohberg, K., Gerhardt, M., Hellmich, A., Hempel, K., Hohage, J., Javorka, P., Klais, J., Koerner, G., Lenski, M., Neu, A., Otterbach, R., Press, P., Reichel, C., Trentsch, M., Trui, B., Salz, H., Schaller, M., Engelmann, H. J., Herzog, O., Ruelke, H., Hubler, P., Stephan, R., Greenlaw, D., Raab, M., and Kepler, N., "Integration and Optimization of Embedded-SiGe. Compressive and Tensile Stressed Liner Films, and Stress Memorization Advanced SOI CMOS Technologies," IEEE International Electron Devices Meeting, pp. 233-236, Dec. 2005.

- [17] Lin, H. N., Chen, H. W., Ko, C. H., Ge, C. H., Lin, H. C., Huang, T. Y., and Lee, W. C., "Channel Backscattering Characteristics of Strained PMOSFETs with Embedded SiGe Source/Drain," IEEE International Electron Devices Meeting, pp. 141-144, Dec. 2005.

- [18] Jan, C. H., Bai, P., Choi, J., Curello, G., Jacobs, S., Jeong, J., Johnson, K., Jones, D., Klopcic, S., and Lin, J., Lindert, N., Lio, A., Natarajan, S., Neirynck, J., Packan, P., Park, J., Post, I., Patel, M., Ramey, S., Reese, P., Rockford, L., Roskowski, A., Sacks, G., Turkot, B., Wang, Y., Wei, L., Yip, J., Young, I., Zhang, K., Zhang, Y., Bohr, M., and Holt, B., "A 65nm Ultra Low Power Logic Platform Technology using Uni-axial Strained Silicon Transistors," IEEE International Electron Devices Meeting, pp. 60-63, Dec. 2005.

- [19] Lwo, B. J. and Wu S. Y., "Calibrate Piezoresistive Stress Sensors Through the Assembled Structure," Journal of Electronic Packaging - Transaction of the ASME, Vol. 125, No. 2, pp. 289-293, 2003.

- [20] Lin. C. Y., Chen, T. S., Lwo, B. J., Chen, Y. S., Ho, T. T., Lee, C. Y., and Kao, C. H., "Calibration of Piezoresistive Stress Sensors in Electronic Packaging," Proceedings of the 6th Symposium Nano Device Technology, pp.173-176, 1999.

- [21] Wu, K. Chang C. S., Lin, H. N., and Lee, W.

- C., "Evaluation of S/D Resistance (RSD) and Strain Scalability by Mechanical-bending Approach," Proceedings of the 14th International Symposium on VLSI Technology, Taiwan, Apr. 2007.

- [22] Wu, K. and Lee, W. C., "Exploring Strain Scalability Using Four-Point Mechanical," Proceedings of the 14th International Symposium on VLSI Technology, Taiwan, Apr. 2007.

- [23] Lwo, B. J., Kao, C. H., Chen, T. S., and Chen, Y. S., "On the Study of Piezoresistive stress Sensors for Microelectronic Packaging," Journal of Electronic Packaging - Transaction of the ASME, Vol. 124, No. 2, pp. 22-26, 2002.