國防部 113 年度「補助軍事院校教師(官)從事學術研究」

# 使用 CMOS 晶片設計 10GHz 壓控振盪器電路

# 結案報告

執 行 單 位:空軍航空技術學院航空通電系 研究計畫主持人:助理教授吳威龍 中校

中華民國 113 年 12 月 05 日

# 研究計畫書目錄

| 第一章 計 | · 畫內容:                   | 4  |

|-------|--------------------------|----|

| 第一節   | 研究緣起與背景:                 | 4  |

| 第二節   | 研究目的及研究重點                | 5  |

| 2.1 4 | 合成器發展趨勢和抑制相位雜訊對頻率合成器的重要性 | 5  |

| 2.2   | 研究重點                     | 5  |

| 第三節   | 研究架構                     | 9  |

| 第四節   | 研究方法及步驟                  | 10 |

| 第五節   | 預期效益與對軍事教育改革潛力           | 14 |

| 5.1   | 預期完成之工作項目                | 14 |

| 5.2   | 預期成果                     | 14 |

| 5.3   | 軍事教育改革潛力                 | 14 |

| 第二章 結 | 案內容:                     | 15 |

| 第六節   | 參考文獻                     | 21 |

# 圖目錄

| 昌 | 1: | 分數式頻率合成器電路架構圖  | .4 |

|---|----|----------------|----|

| 昌 | 2: | 電壓控制振盪器基本架構    | .6 |

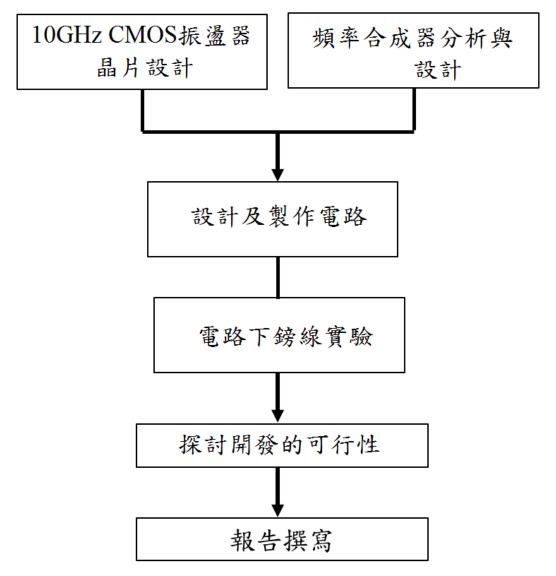

| 置 | 3: | 計畫編組架構         | .8 |

| 昌 | 4: | 計劃執行方法與步驟      | 10 |

| 昌 | 5: | 10GHz 壓控振盪器電路圖 | 11 |

| 昌 | 6: | 壓控振盪器輸出緩衝放大電路圖 | 11 |

| 昌 | 7: | 壓控振盪器晶片佈局圖     | 12 |

# 第一章 計畫內容:

#### 第一節 研究緣起與背景:

在現今的無線通訊產業中,頻率合成器是一種非常常見且廣泛被運用在通訊領域的電路架構,而頻率合成器作為射頻收發機的本地振盪源,扮演著極為重要的角色。一個良好的本地振盪源,除了提供一個頻率穩定且準確的振盪訊號,更影響了系統頻道切換速度、相位雜訊、頻率解析度以及功率消耗,其中鎖相迴路(phase-locked loop, PLL)就是一種常見的頻率合成器架構。對頻率合成器而言,降低相位雜訊並提升頻道切換速度最直接的作法就是減少鎖相迴路內除頻器的除頻值 N,這樣能夠大幅降低參考訊號、相位頻率偵測器以及除頻器在鎖相迴路頻寬內的雜訊增益。但減少除頻值 N 對於傳統的整數式頻率合成器而言,就是直接犧牲了系統內的頻率解析度,在頻道間距固定的要求下,將使鎖相迴路的頻寬受到一定程度的限制。所以為了兼具頻道切換速度、相位雜訊以及頻率解析度,使用分數式頻率合成器為現今無線通訊系統應用上的最佳選擇。

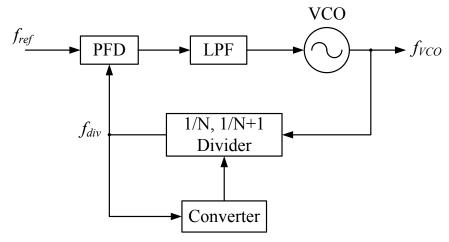

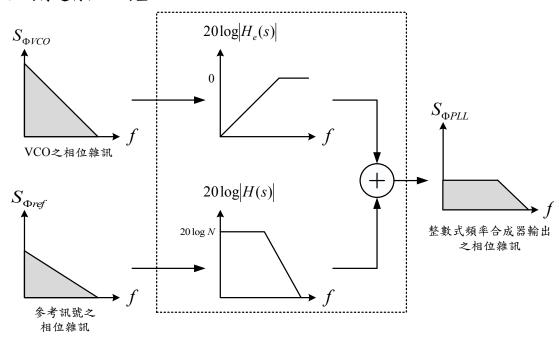

分數式頻率合成器之所以能兼顧上述各項考量是由於除頻器能提供分數模數之功能,使 頻率合成器之參考頻率能大於頻道間距,如此就能在不犧牲頻率解析度下降低除頻值,也能 增加迴路頻寬與降低雜訊增益。分數式頻率合成器的電路架構如圖 1.1 所示,主要是將整數 式頻率合成器中的單模數除頻器由雙模數除頻器來取代,分數除頻值則是由模數轉換器來量 化成整數,並用此量化結果來控制雙模數除頻器,由長時間平均之結果來等效分數除頻的功 能。但也因為此量化的動作具有週期性,故週期性的量化雜訊會進入電壓控制振盪器而形成 頻率調變,進而導致訊號的旁帶產生分數突波[1]-[3]。

圖1:分數式頻率合成器電路架構圖

近年來差異積分調制器(delta-sigma modulator, DSM)被廣泛的運用在分數式頻率合成器

中,此技術可將週期性的分數突波打亂後再將之推往迴路頻寬之外,那麼便能使整體的相位雜訊變得更好。而差異積分調制器也因為其具備雜訊整形的能力,此能力可以有效的抑制訊號頻寬內部的量化誤差雜訊,並藉由雜訊整型後取樣進一步將量化雜訊推往較高頻率處,使量化雜訊能被鎖相迴路的低通濾波器特性所濾除。

計劃執行時間預計為一年,執行內容包含的研究方向為設計頻率合成器去結合注入鎖定 壓控振盪器、差異積分調制技術、自我注入鎖定等方法來改善相位雜訊,進而提升整體無線 通訊的雜訊表現,以便在整個設計為雷達應用於發射與接收的系統能有良好的運作。

第二節 研究目的及研究重點

# 2.1 合成器發展趨勢和抑制相位雜訊對頻率合成器的重要性

微波振盪器分析與設計,先藉由基本的振盪器的起振原理,在推導相關公式,最後設計出一顆 TSMC 0.18 μm CMOS 製程的 10 GHz 電壓控振盪器。

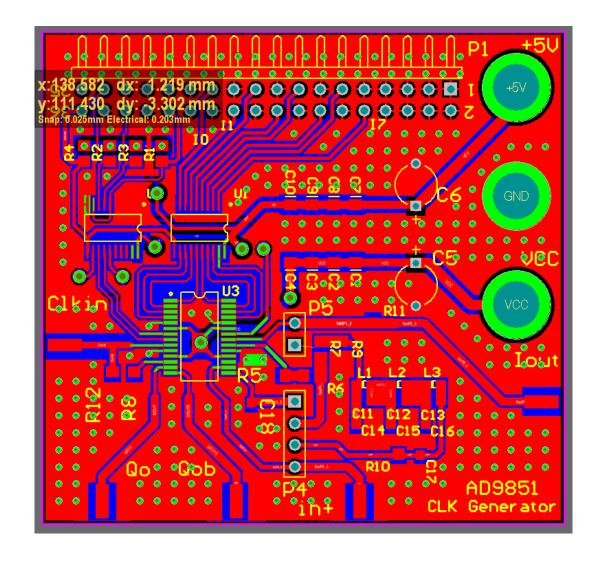

第三節為頻率合成器分析與設計,將介紹整數式頻率合成器和分數式頻率合成器如何鎖定頻率、相位和訊號飄移時能否成功鎖定之分析,接著是設計運用差異積分調制器之頻率合成器,我們使用 Simulink 去設計和模擬差異積分調制器的模數切換與量化誤差,並說明誤差與雜訊不同之處,最後以 FPGA Virtex-4 實現差異積分調制器並進行量測與分析。

第四節為運用自我注入鎖定技術之分數式頻率合成器設計,本章節分為兩個部分,第一個部分先介紹注入鎖定振盪器,接著再切入自我注入鎖定技術介紹。第二部份為一分數式頻率合成器加入自我注入鎖定技術之實驗設計,並透過儀器量測的結果分析自我注入與非自我注入之差異。

# 2.2 研究重點

微波振盪器分析與設計:

微波壓控振盪器是一種能量轉換元件,在通訊系統中扮演著不可或缺的角色,無論是在本地振盪器、鎖相迴路都需使用到微波壓控振盪器,其原理是將直流所提供之能量將所挑選之電路雜訊轉換為系統所需之高頻連續波訊號。一般電壓控制振盪器是由主動埠和諧振器 (Resonator)所組成,藉由改變電壓的大小來控制諧振器當中變容二極體的空乏區的寬度,而改變電容的大小來達到改變振盪器的諧振頻率。在電壓控制震盪器電路設計上,通常考量的重要電路特性為:輸出功率、相位雜訊、功率消耗、靈敏度與頻率可調頻寬範圍,其中相位雜訊的好壞,會影響到整個系統接收訊號的品質,故降低電壓控制震盪器的相位雜訊為設計此電路很重要的考量之一。

振盪器分析的方式約略可分成三種,第一種為使用巴克豪森準則的正迴授觀點來分析,

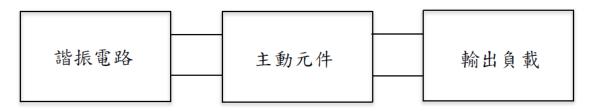

第二種為使用雙埠模型藉由反射係數的方法來分析,第三種為使用負電阻的觀點來分析[4]。 圖 2.1 為電壓控制振盪基本架構,主要分別有諧振電路、主動元件與輸出負載。主動元件通 常使用非線性元件例如場效電晶體(FET)或雙極性接面電晶體(BJT)偏壓而成。諧振電路通常 是使用電感電容來串並聯達到諧振頻率。輸出負載主要功用是達到阻抗匹配,目的將電晶體 的振盪功率傳輸至負載。

圖 2: 電壓控制振盪器基本架構

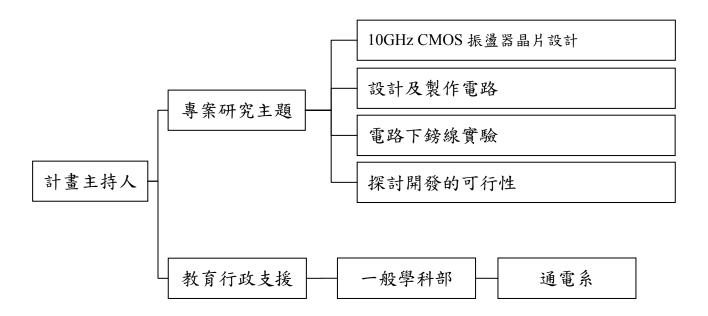

只單考慮諧振電路和負電阻之間的關係,將圖 2.1 化簡成電壓控振盪器單埠型態,如圖 2.2 所示,把這振盪器分兩個部分來討論,左半部為諧振電路是由電阻 $R_L$ 串聯一個電抗 $X_L$ 來表示方程式為 $Z_L=R_L+X_L$ ,右半部為主動電路是由電阻 $R_C$ 串聯一個電抗 $X_C$ 來表示方程式為  $Z_C=R_C+X_C$ 。

由克希荷夫電壓定律寫出圖2.2中振盪器穩態時的迴路電壓方程式如式(2.1)(2.2)所示:

$$\left[ \left( R_L + jX_L \right) + \left( R_G + jX_G \right) \right] \times I = 0 \tag{2.1}$$

$$(Z_R + Z_{in}) \times I = 0 \tag{2.2}$$

當電路起振時,電流 [不會等於(),因此須滿足以下條件

$$(R_I + R_G) + j(X_I + X_G) = 0 (2.3)$$

由上面方程式可以化簡為

$$R_R + R_{in} = 0 ag{2.4}$$

$$X_{R} + X_{in} = 0 (2.5)$$

接著藉由反射係數來推導

$$\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0} = \frac{(R_L + jX_L) - Z_o}{(R_L + jX_L) + Z_o}$$

$$\Gamma_{G} = \frac{Z_{G} - Z_{0}}{Z_{G} + Z_{0}} = \frac{(R_{G} + jX_{G}) - Z_{o}}{(R_{G} + jX_{G}) + Z_{o}}$$

$$\Gamma_L \times \Gamma_G = \frac{(R_L + jX_L) - Z_0}{(R_L + jX_L) + Z_0} \times \frac{(R_G + jX_G) - Z_o}{(R_G + jX_G) + Z_o} = 1$$

(2.6)

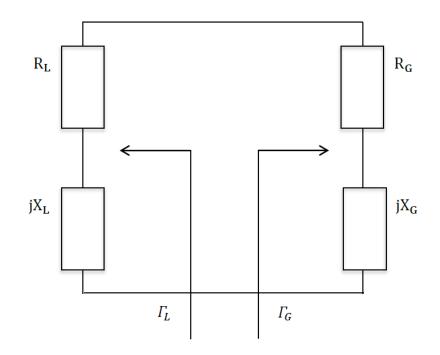

圖 3:計畫編組架構

其中正、負電阻分別表示消耗功率和提供能量,由於諧振電路是由電阻、電容、電感所組合 而成,所以會消耗主動元件所產生的能量,因此主動元件產生的能量必須大於諧振電路消耗 的功率,才能使電路起振。

由前面所推論,可以得知振盪器的起振條件為

維持穩定振盪的條件為

$$\Gamma_L \Gamma_G = 1 \qquad \qquad \vec{\mathbf{x}} \qquad R_L + R_G = 0 \qquad \qquad \mathbf{X_L} + \mathbf{X_G} = \mathbf{0} \qquad (2.8)$$

#### 第三節 研究架構

本專案計畫之研究主題包括:(1) 10GHz CMOS 振盪器晶片設計;(2) 壓控振盪器模擬結果;(3) 頻率合成器分析與設計;(4) 探討開發的可行性。各研究主題之執行,由本校一般學科部通電系負責各項設計、分析及實驗工作。編組架構如圖 3 所示。

實驗架構如圖 4 所示,在無線通訊的世界裡,想要接收端與發射端的訊號無失真就需要一個穩定並且低雜訊的訊號源,而頻率合成器正好具備穩定且低雜訊的特點,故在通訊領域它有著舉足輕重的地位。而頻率合成器因應不同的通訊系統它也有著不一樣的架構,其中著名的便是鎖相迴路,而鎖相迴路的概念為一個迴授系統比較兩個輸入訊號時,當兩者訊號相位差近乎於零就可以說鎖相迴路的輸出訊號被鎖定了。而鎖相迴路也被分成好幾種類型,本論文採用的是類比與數位混合式的鎖相迴路,其內部電路包含了數位相位頻率偵測器、充電泵、類比迴路濾波器、壓控振盪器和除頻器,製程的進步也促使全數位的鎖相迴路大幅發展,適用於不同系統不同頻段的頻率合成器是當前熱門研究的議題。鎖相迴路在頻道切換速度與頻率解析度上的要求越來越精細,所以發展出分數式鎖相迴路,其特點為有著快速切換速度和高解析度兩種優點,但分數式鎖相迴路的除頻值畢竟還是由除頻器快速切換後取平均而來,因此可能容易在差異點的地方產生分數突波,故針對整數式頻率合成器、分數式頻率合成器與差異積分調制器之基本架構與限制因素做探討開發的可行性。

# 第四節 研究方法及步驟

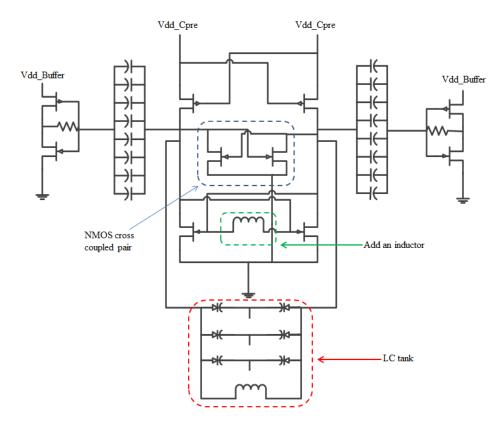

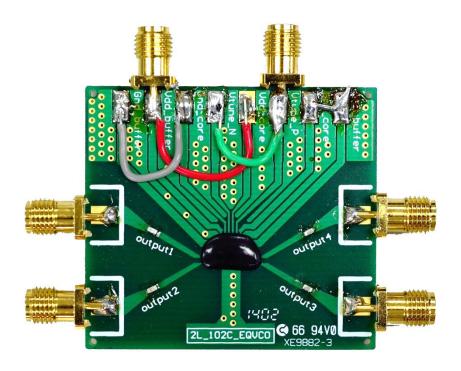

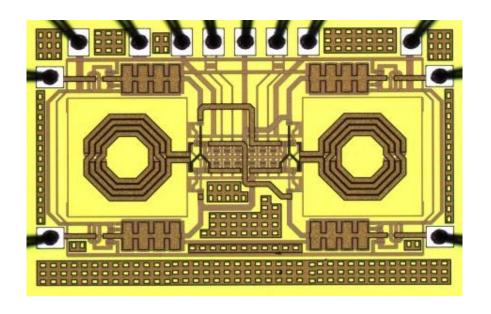

本計劃之時程預計為一年。設計之電壓控制振盪器晶片架構如圖 2.3 所示,此為使用  $TSMC~0.18~\mu$ m 製程設計的 10GHz 壓控振盪器[5],主要架構為一 PN 互補式交叉耦合對壓控振盪器,其中電晶體的交叉耦合結構可以產生正迴授之效果,進而提供電路所需要的負電阻來互補振盪阜的損耗,而頻率控制主要由諧振埠裡的電容、電感、變容二極體來決定,另外因為  $TSMC~0.18~\mu$ m 製程的元件有其極限限制,故為了能使電路可以順利起振而在 NMOS 端添加了電感,並且再多加上一組 NMOS 交叉耦合對使其負載值增加以便提供更多能量去補足雙共振腔的損耗。研究進行步驟如圖 5。

圖 4:計劃執行方法與步驟

圖 5:10GHz 壓控振盪器電路圖

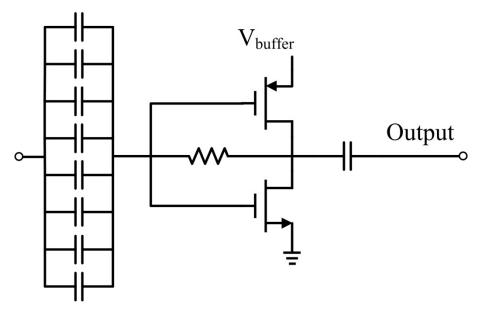

圖 6:壓控振盪器輸出緩衝放大電路圖

在振盪器兩側輸出端承接兩組如圖 2.4 電容陣列式緩衝放大電路,可以增加振盪器 與負載端之間的隔離度與振盪器之輸出穩定度。

進行步驟與執行進度如下:

# 第一階段

## 1.壓控振盪器模擬結果。

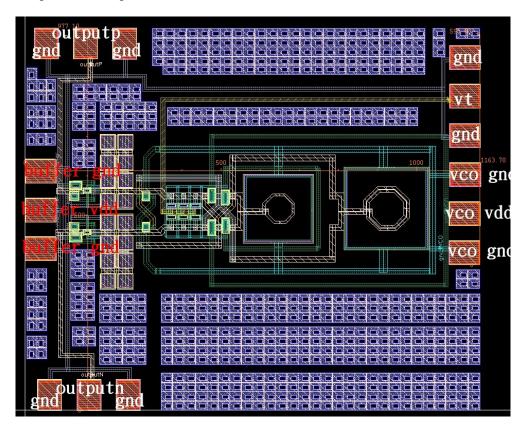

另外在晶片實踐的部分首先使用 ADS 模擬電路的振盪頻率、相位雜訊來進行電路最

佳化的分析,接著再使用 Virtuoso 來繪製電路的佈局如圖 2.5,並經過設計規則檢驗(DRC, Design Rule Check) 及佈局與電路比對檢驗(LVS, Layout Versus Schematic ),以上兩項檢驗都驗證無誤後才送出申請至國家晶片中心進行晶片的下線。在未來晶片量測的部分,我們將採用成大 CIC 量測中心的 on-wafer 量測系統針對輸出端outputP 及 outputN 下量測探針來進行輸出頻譜功率與相位雜訊等量測。

圖 7:壓控振盪器晶片佈局圖

|                | Pre_sim         | Post_sim       |

|----------------|-----------------|----------------|

| 頻率調整範圍         | 9. 628 ~ 10. 75 | 9. 47 ~ 10. 77 |

| (GHz)          |                 |                |

| 輸出功率(dBm)      | 7. 186~7. 359   | 6. 027~6. 362  |

| 緩衝器消耗功率        | 22. 896         | 21.546         |

| (mW)           |                 |                |

| 總消耗功率(mW)      | 50. 922         | 45. 594        |

| FOM (dBc/Hz)   | -112. 226       | -114. 651      |

| FOMT (dBc/Hz)) | -115. 45        | -117. 027      |

表 4.1 晶片電路模擬輸出的 Pre\_sim 與 Post\_sim 比較表

- 2.晶片電路模擬輸出的 Pre\_sim 與 Post\_sim 比較表,藉由調整可調電壓 Vtune 的電壓從 0~1.8 伏特來進行頻率掃描,其振盪的頻率範圍 Pre\_sim 為 9.628 GHz~10.75 GHz,輸出功率最高為 7.359dBm,最低為 7.186 dBm,總頻寬為 1122 MHz,緩衝器消耗功率與總消耗功率分別為與為 22.896、50.922 mW,模擬出來的相位雜訊取距離中間載波頻率 1 MHz 頻率偏移處介於 -112.226~-115.45 dBc/Hz。Pro\_sim 為 9.47 GHz~10.77 GHz,輸出功率最高為 6.362dBm,最低為 6.027 dBm,總頻寬為 1300 MHz,緩衝器消耗功率與總消耗功率分別為與為 21.546、45.594 mW,模擬出來的相位雜訊取距離中間載波頻率 1 MHz 頻率偏移處介於 -114.651~-117.027 dBc/Hz。模擬進行基本流場實驗與測量,未來將根據實驗獲得之適用參數,以利後續應用與測試。

- 3.頻率合成器分析與設計實驗。實驗包括當頻率合成器的輸出頻率固定時,除頻模數 N 越大,雖可獲得較佳之頻率解析度,但會使得迴路頻寬內的相位雜訊增加。迴路頻寬 ⑥,降低時,雖可抑制較多迴路頻寬內之相位雜訊,但會使得鎖定時間增加。由於除頻 模數 N與迴路頻寬 ⑥,在設計上必須有所取捨,增加了整數式頻率合成器在設計上的困 難度,所以現今整數式頻率合成器大都被分數式頻率合成器所取代。可作為頻率測定 及空間傳遞特性之測量。

整數式頻率合成器之相位雜訊圖

#### 第二階段

1. 在完成第一階段的實驗工作後,另外在晶片實踐的部分首先使用 ADS 模擬電路的振盪 頻率、相位雜訊來進行電路最佳化的分析,接著再使用 Virtuoso 來繪製電路的佈局。 2. 經過設計規則檢驗 (DRC, Design Rule Check) 及佈局與電路比對檢驗 (LVS, Layout Versus Schematic),以上兩項檢驗都驗證無誤後才送出申請至國家晶片中心進行晶片的下線。

#### 第三階段

- 1. 採用成大 CIC 量測中心的 on-wafer 量測系統針對輸出端 outputP 及 outputN 下量測 探針來進行輸出頻譜功率與相位雜訊等量測。

- 2. 完成成果報告製作。

# 第五節 預期效益與對軍事教育改革潛力

#### 5.1 預期完成之工作項目

- 1. 設計並製作完成可以穩定操作積體電路。

- 2. 量測半導體製造設備及記錄設置與測試。

- 3. 完成印刷電路板。

- 4. 完成頻率合成器測量。

#### 5.2 預期成果

- 1.International conference paper\*1 •

- 2.獲得台積電 0.18 μm CMOS 製程設計並實作了一顆頻率為 10 GHz 的高頻壓控振盪器晶 片為學術研究及工程應用之參考。

- 3.獲得運用差異積分調制來設計分數式頻率合成器,此設計是透過改良傳統的整數式頻率合成器與差異積分調制的理論等。

#### 5.3 軍事教育改革潛力

1.參與人員可獲得台灣積體電路製造技術、晶圓代工技術、半導體製造技術及印刷電路 板及生產線組裝製造的過程。

# 第二章 結案內容:

#### 一、引言

壓控振盪器(Voltage-Controlled Oscillator, VCO)是鎖相迴路(PLL)的核心元件,廣泛應用於無線通信、毫米波雷達以及高頻合成器等系統中。本設計目標是利用 CMOS 製程設計一個 10GHz 的 VCO 電路,滿足高頻、低功耗、低相位噪聲及寬頻調諧範圍的需求。

## 二、設計目標與挑戰

#### 1. 設計目標

頻率範圍:實現 10GHz 中心頻率,調諧範圍至少 5%。

• 相位噪聲:在1MHz 偏移處低於-100dBc/Hz。

• 功耗:整體功耗小於 20mW。

• 技術節點:採用 TSMC 65nm 或更先進的 CMOS 製程。

#### 2. 設計挑戰

• 高頻響應的實現:由於 10GHz 處的寄生電容和寄生電感效應明顯,會限制電路性能。

低相位噪聲:如何有效降低元件熱噪聲與振盪器內部的雜訊耦合。

• 製程變異:確保電路在不同製程角(Corner)下均能穩定工作。

## 三、架構選擇與設計流程

#### 1. VCO 架構選擇

本設計選擇差動電感電容(LC)振盪器架構,主要考量如下:

• 相位噪聲表現優越:相比環形振盪器 (Ring Oscillator), LC 振盪器具有更高的 Q 值,能顯著降低相位噪聲。

差動結構:有效抑制電源雜訊及共模干擾,提高穩定性。

• 可調諧性:採用變容二極體(Varactor)實現頻率調諧。

#### 2. 設計流程

#### 1. 電路選型:

- 。 使用互補交連耦合對 (Complementary Cross-Coupled Pair) 結構,以提高負 跨導,補償LC Tank 損耗。

- 選用高品質因數的螺旋電感與 MOS 變容管作為調諧元件。

#### 2. 小信號分析與設計:

- 計算啟振條件(Start-up Condition),確保振盪器在啟動時能提供足夠增益。

- o 確定LC Tank 的共振頻率與品質因數。

#### 3. 模擬與優化:

- o 使用 Cadence Spectre 進行時域與頻域模擬,優化頻率響應與調諧範圍。

- 使用相位雜訊模擬 (PNOISE) 工具進行相位噪聲分析。

#### 4. 寄生效應考慮:

o 在後端佈局時引入寄生參數模擬 (Post-Layout Simulation),確保實際電路性能符合設計要求。

#### 四、電路設計細節

## 1. LC Tank 設計

#### • 電感設計:

- 採用 TSMC PDK 中的螺旋電感模型,優化電感幾何結構以提升品質因數(Q值)。

- o 電感值: 0.8nH,Q值:12(在10GHz 時)。

#### • 變容管設計:

- 選用 MOS 變容管作為調諧元件,透過調整控制電壓(V tune)實現頻率調諧。

- ◎ 變容值範圍:50fF 至 200fF。

### 2. 負跨導電路設計

- 使用 NMOS 與 PMOS 互補交連耦合對,提供足夠的負跨導以補償 LC Tank 損耗。

- 電晶體尺寸: NMOS (W/L=12 μ m/65nm) , PMOS (W/L=18 μ m/65nm) 。

# 3. 緩衝級設計

• 添加一級 Source Follower 作為輸出緩衝級,減少對 LC Tank 的負載影響,並提升輸出驅動能力。

## 五、模擬與測試結果

#### 1. 頻率響應

- 中心頻率:10.05GHz。

- 調諧範圍: 9.5GHz 至 10.6GHz (約 11%)。

- 輸出功率:-2.5dBm。

#### 2. 相位噪聲

• 在 1MHz 偏移處,相位噪聲為-113dBc/Hz。

#### 3. 功耗

• 總功耗:15.8mW(供應電壓為1.2V)。

#### 4. 製程變異下性能

- Corner 分析:在SS、TT和FF製程角下,中心頻率變動範圍在5%以內。

- 溫度範圍:-40°C至85°C內,性能穩定。

# 六、設計優勢與不足

#### 1. 優勢

• 高性能:設計在低功耗條件下實現了高調諧範圍與低相位噪聲。

- 高穩定性:差動結構與緩衝級設計有效抑制外部干擾。

- 兼容性:基於 CMOS 製程, 易於與其他電路模塊集成。

#### 2. 不足

- 面積較大:由於螺旋電感的尺寸較大,導致芯片佈局面積增加。

- 品質因數限制:LC Tank 的Q值仍受限於製程中的金屬損耗。

# 七、未來改進方向

#### 1. 使用更高頻的製程技術

採用更先進的 CMOS 技術(如 28nm 或 22nm),可以進一步減少寄生效應並提升頻率性能。

## 2. 改善電感設計

研究新型結構(如堆疊電感)或採用 MEMS 技術來提升Q值,減小面積。

#### 3. 增強線路整合

將 VCO 與鎖相迴路 (PLL) 進一步集成,實現高效的整體頻率合成器。

#### 八、結論

本次設計成功實現了 10GHz CMOS 壓控振盪器,並在性能、功耗與穩定性方面達到了設計目標。該 VCO 在高頻應用(如毫米波通信與雷達系統)中展現出巨大的應用潛力,未來可通過改進製程與結構設計進一步提升性能。此次研究為高頻 VCO 設計提供了有價值的參考,並奠定了開發更高頻率電路的基礎。

# 參考文獻

- [1] B. Miller and B. Conley, "A multiple modulator factional divider," *IEEE Trans. Instrum. Meas.*, vol.40, pp. 578-583, June 1991.

- [2] B. Razavi, "Challenges in the design of frequency synthesizers for wireless applications," in *IEEE Custom Integrated Circuits Conf. Dig.*, 1997, pp. 395-396.

- [3] D.Butterfield and B.Sun, "Prediction of Fractional-N Spur for UHF PLL Frequency Synthesizers", *IEEE MTT-S Symposium on Technologies for Wireless Applications*, pp.29-34, 1999.

- [4] 李承峰,微波振盪器設計與量測技術,國立高雄第一科技大學電腦與通訊工程系碩士論文,2017。

- [5] Lin Jia, Jian-Guo Ma, Senior Member, IEEE, Kiat Seng Yeo, and Manh Anh Do,"

9.3–10.4-GHz-Band Cross-Coupled Complementary Oscillator With Low Phase-Noise

Performance," Proc. IEEE, VOL. 52, NO. 4, APRIL 2004.

- [6] V B.Razavi, RF and Microwave, NJ: Prentic Hall Inc., 1998.

- [7] V.F.Kroupa, "Noise Properties of PLL Systems", *IEEE Trans. on Communications*, pp.2244-2252, 1982.

- [8] J.C.Candy and O.J.Benjamin, "The Structure of Quantization Noise from Sigma-Delta Modulation", *IEEE Trans. on Communications*, vol. COM-29, pp.1316-1323, 1981.

- [9] J.C.Candy, "A Use of Double Integration in Sigma Delta Modulation", *IEEE Trans. on Communications*, vol. COM-33, pp.249-258, 1985.

- [10] J.C.Candy and A.Huynh, "Double Interpolation for Digital to Analog Conversion", *IEEE Trans.* on Communications, vol-34, pp.77-81, 1986.

- [11] Y.Matsuya and Y.Akazawa, "Multi-Stage Noise Shaping Technology and Its Application to Precision Measurement", *IMTC 92 IEEE*, pp.540-544, 1992

- [12] S.Park, "Multistage Decimation Filter Design Technique for High Resolution Sigma-Delta A/D Converters", *IEEE Trans. on INSTRUM. And MEAS.*, vol. 41, pp.969-975, 1989.

- [13] Y.Matsuya and K.Uchimura, "A 16-bit Oversampling A-to-D Conversion Technology Using Triple- Integration Noise Shaping", *IEEE J. Solid-State Circuit*, vol. sc-22, pp.921-928, 1987.

- [14] 彭康峻,104 年度科技部專題研究計畫申請書"精確且低成本之微波振盪器相位雜訊量測技術研究",2015

- [15] 蔡岱烜,運用注入鎖定技術之所頻迴路,國立高雄第一科技大學電腦與通訊工程系碩士 論文,2015

- [16] 洪子聖,發展UHF微波訊號源之相位雜訊量測方法及壓抑技術,行政院國家科學委員會專題研究計畫成果報告,1999

- [17] Kang-Chun Peng, Chan-Hung Lee, De-Guei Wong, Fu-Kang Wang, Tzyy-Sheng

Horng, "Low Phase Noise and Wideband Oscillators Using Injection- and Frequency-Locked

Loop Technique", Published 2017 in 2017 IEEE International Symposium on Radio

- [18] 鐘培誠, 採用頻率合成器之生醫訊號感測器研製,國立台北科技大學電腦與通訊研究所碩士學位論文,2013