國防部 113 年度「補助軍事院校教師(官)從事學術研究」

# 24GHz 相位雷達系統量測

# 結案報告

執 行 單 位:空軍航空技術學院航空通電系 研究計畫主持人:助理教授吳威龍 中校

中華民國 113 年 12 月 05 日

# 研究計畫書目錄

| 第 | 一章言 | 計畫內容:             | 4   |

|---|-----|-------------------|-----|

|   | 第一節 | 研究緣起與背景:          | 4   |

|   | 第二節 | 研究目的及研究重點         | 6   |

|   | 2.1 | 頻率合成器去結合注入鎖定壓控振盪器 | 6   |

|   | 2.2 | 研究重點              | 7   |

|   | 第三節 | 研究方法及步驟           | .11 |

|   | 第四節 | 預期效益與對軍事教育改革潛力    | 12  |

|   | 4.1 | 預期完成之工作項目         | 12  |

|   | 4.2 | 預期成果              | 12  |

|   | 4.3 | 軍事教育改革潛力          | 13  |

|   | 第五節 | <b>結案報告</b>       | 18  |

# 圖目錄

| 啚 | 1: | 鎖相迴路電路方塊                 | 4  |

|---|----|--------------------------|----|

| 邑 | 2: | 線性非時變鎖相迴路模型              | 5  |

| 邑 | 3: | 數位信號轉換成類比信號              | 5  |

| 圖 | 45 | 的振盪現象                    | 6  |

| 啚 | 5: | 注入鎖定壓控振盪器等效模型            | 8  |

| 置 | 6: | 注入鎖定之設置(a)旋轉器 (b) T 型偏壓器 | 8  |

| 昌 | 7: | 相位檢測器                    | 9  |

| 邑 | 8: | 延遲線頻率鑑別器                 | 9  |

| 邑 | 9: | 運用延遲線之傳統鎖頻迴路             | 10 |

| 邑 | 10 | :計畫編組架構                  | 10 |

| 邑 | 11 | :計畫之進行步驟流程方塊圖            | 11 |

| 昌 | 12 | :相位陣列元件基礎理論圖             | 12 |

## 第一章 計畫內容:

### 第一節 研究緣起與背景:

雷達應用始於十九世紀,當時主要的用途是用於戰爭中偵測敵軍飛機與船隻動向 [1] [2],直到二次戰爭後,雷達系統才開始普遍應用在日常生活中。雷達主要讓我們用來測速度以及距離,時至今日,雷達的應用遍及行車交通 [3]、颱風觀測 [4]、地震救災 [5] [6] 等。其中,最常用到的領域是在醫療診斷的部分,醫護人員會為了看診或是檢查胎兒,亦或是確認重症病患的心跳穩定而必須取得病人的 [7] [8]。一般測量心跳的方式是將導極貼片貼於身上,並在四肢夾上導程夾,使用儀器測得,然而,這個方法並不適用於身上有大片傷口的人,因為導極貼片很可能受傷口渗出的組織液汙染,也可能在從撕下貼片的過程中再次傷到傷口。遇到這種狀況就得採用免接觸式的測量方式,這種方式就是使用都普勒雷達測量 [9],除了應用在大片傷口的患者,還可用於需要長照的老人、剛出生的嬰兒、和患有睡眠呼吸中止症的人 [10]。現在正值新冠肺炎疫情期間,盡量減少與病患直接接觸成為一個需要被納入的考量,因此非接觸式的測量方式在未來的醫療方面的使用將更廣泛。

應用在生理檢測的都普勒雷達是運用都普勒效應的特性來測得受測者的,測量方式為由雷達的發射端藉由天線發射出電波,電波傳播至受測者的身體後反射回雷達的接收端,藉由人體呼吸以及心臟跳動時產生的胸腔起伏改變來得到受測者的呼吸與心跳頻率。但是,要使用都普勒雷達來測量需要克服會降低雷達靈敏度的一些問題,都普勒雷達的相關文獻裡提及,硬體設備會產生直流偏移[11],靜態雜波反射會造成範圍相關效應(雷達會用到[12])以及相位雜訊(pll [13),還有雷達測量時產生的空檢測點(IQ正交解調器[14]),都是需要克服的障礙。

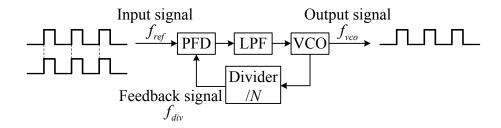

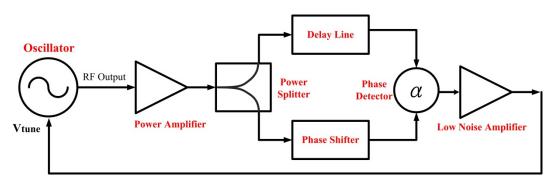

本研究是使用經過 IQ 正交解調系統的天線雷達偵測人體的呼吸與心跳,讓輸入之訊號源經過鎖相迴路電路抑制相位雜訊後,經由向量訊號模組取得量測之數據,再將數據載入matlab 進行傅立葉轉換與濾波處理,藉此得到實驗結果,最後再與沒經過鎖相迴路電路的訊號源以及單用儀器訊號源的實驗組做比較,由此得到實驗結論,如圖1所示。

圖1:鎖相迴路電路方塊

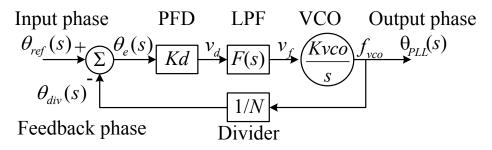

圖2:線性非時變鎖相迴路模型

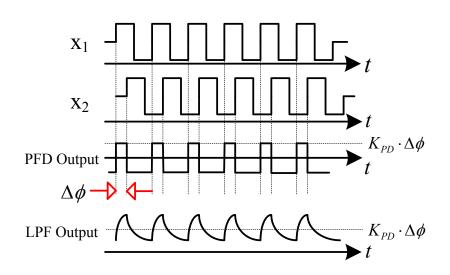

如圖 2 所示,鎖相迴路架構中有四個元件:壓控振盪器、迴路濾波器(loop filter)、相位頻率檢測器(phase frequency detector, PFD)和除頻器(frequency divider)。其系統運作原理為相位頻率檢測器加上石英振盪器所產生的訊號為參考訊號,再與壓控振盪器所產生的訊號,再次由除頻器產生除數後前後比較結果,經過輸出後的誤差值訊號由迴路濾波器訊號的中高頻成份濾除,最後留下低頻訊號控制調整壓控振盪器頻率輸出,系統最後將參考訊號與壓控振盪器除頻後的相位誤差。接著 PFD 輸出波形是脈衝波,原因是比較兩信號的正緣觸發,又是直流輸出,因而形成類似數位信號,所以希望將之轉換成類比信號,便以使用低通濾波器(LPF)的充放電來完成,如圖 3 所示,PFD 會輸出些微變化的直流,因相位差關係,脈波寬度也會增減,而 LPF 的輸出則用脈波寬度判斷,以 PFD 輸出電壓為基礎來增減電壓。

圖3:數位信號轉換成類比信號

系統中的相位誤差當趨近逾零時,使參考訊號及壓控振盪器除頻達到同步且相位頻率鎖 定,推理輸出頻率為

$$f_{vco} = N \cdot f_{ref} \,. \tag{1.1}$$

鎖相迴路鎖定時設為整個鎖相迴路系統為線性非時變,以拉氏轉換(laplace transform)分析推導迴路轉移函數。如圖 4.2 所式,其中相位頻率檢測器增益表示 Kd,單位為 V/rad;迴路濾波器之轉移函數表示 F(s);壓控振盪器增益表示 Kvco;參考訊號相位表示 $\theta_{ref}(s)$ ;壓控振盪器相位及除頻後相位表示為 $\theta_{vco}(s)$ 、 $\theta_{div}(s)$ ;兩個同時輸入訊號相位差異則表示 $\theta_{e}(s)$

計劃執行時間預計為一年,執行內容包含的研究方向為設計鎖相迴路鎖定時設為整個鎖相迴路系統為線性非時變,以拉氏轉換(laplace transform)分析推導迴路轉移函數,差異積分調制器(delta-sigma modulator, DSM)被廣泛的運用在分數式頻率合成器中,此技術可將週期性的分數突波打亂後再將之推往迴路頻寬之外,那麼便能使整體的相位雜訊變得更好。而差異積分調制器也因為其具備雜訊整形的能力,此能力可以有效的抑制訊號頻寬內部的量化誤差雜訊,並藉由雜訊整型後取樣進一步將量化雜訊推往較高頻率處,使量化雜訊能被鎖相迴路的低通濾波器特性所濾除,以便在整個設計為雷達應用於發射與接收的系統能有良好的運作。

第二節 研究目的及研究重點

# 2.1 頻率合成器去結合注入鎖定壓控振盪器

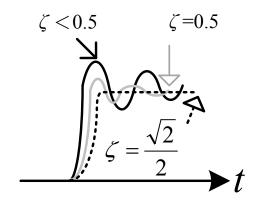

實際受欠阻尼響應(underdamped)可知最快穩定時間與低通濾波器極點和 $\zeta$ 有關,亦是指 迴路頻寬越大越能提早穩定。但 $\zeta$ 的值太小會有嚴重振盪現象, $\zeta$  需盡可能的小,然後衡量 $\zeta$  振盪現象,通常 $\zeta$ 最佳的值為 0.5 或 0.707。如圖 4 所示。

圖4<sup>5</sup>的振盪現象

# 2.2 研究重點

雷達應用始於十九世紀,當時主要的用途是用於戰爭中偵測敵軍飛機與船隻動向 [1] [2],直到二次戰爭後,雷達系統才開始普遍應用在日常生活中。雷達主要讓我們用來測速度以及距離,時至今日,雷達的應用遍及行車交通 [3]、颱風觀測 [4]、地震救災 [5] [6] 等。其中,最常用到的領域是在醫療診斷的部分,醫護人員會為了看診或是檢查胎兒,亦或是確認重症病患的心跳穩定而必須取得病人的 [7] [8]。一般測量心跳的方式是將導極貼片貼於身上,並在四肢夾上導程夾,使用儀器測得,然而,這個方法並不適用於身上有大片傷口的人,因為導極貼片很可能受傷口滲出的組織液汙染,也可能在從撕下貼片的過程中再次傷到傷口。遇到這種狀況就得採用免接觸式的測量方式,這種方式就是使用都普勒雷達測量 [9],除了應用在大片傷口的患者,還可用於需要長照的老人、剛出生的嬰兒、和患有睡眠呼吸中止症的人 [10]。現在正值新冠肺炎疫情期間,盡量減少與病患直接接觸成為一個需要被納入的考量,因此非接觸式的測量方式在未來的醫療方面的使用將更廣泛。

應用在生理檢測的都普勒雷達是運用都普勒效應的特性來測得受測者的,測量方式為由雷達的發射端藉由天線發射出電波,電波傳播至受測者的身體後反射回雷達的接收端,藉由人體呼吸以及心臟跳動時產生的胸腔起伏改變來得到受測者的呼吸與心跳頻率。但是,要使用都普勒雷達來測量需要克服會降低雷達靈敏度的一些問題,都普勒雷達的相關文獻裡提及,硬體設備會產生直流偏移[11],靜態雜波反射會造成範圍相關效應(雷達會用到[12])以及相位雜訊(pll [13),還有雷達測量時產生的空檢測點(IQ正交解調器[14]),都是需要克服的障礙。

鎖相迴路架構中有四個元件:壓控振盪器、迴路濾波器(loop filter)、相位頻率檢測器(phase frequency detector, PFD)和除頻器(frequency divider)。其系統運作原理為相位頻率檢測器加上石英振盪器所產生的訊號為參考訊號,再與壓控振盪器所產生的訊號,再次由除頻器產生除數後前後比較結果,經過輸出後的誤差值訊號由迴路濾波器訊號的中高頻成份濾除,最後留下低頻訊號控制調整壓控振盪器頻率輸出,系統最後將參考訊號與壓控振盪器除頻後的相位誤差。

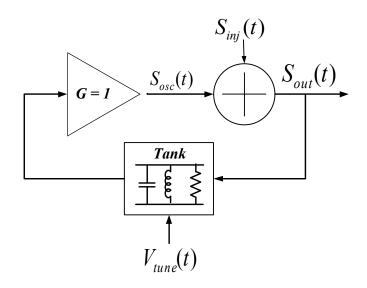

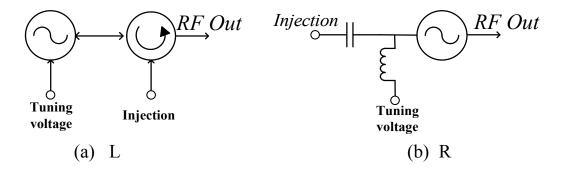

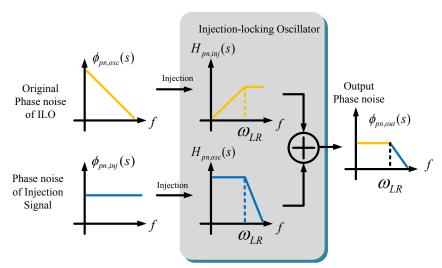

傳統的微波振盪器,再額外加入注入鎖定訊號,構成如圖 5 所示注入鎖定壓控振盪器等效模型,進而分析注入鎖定電壓控制振盪器之相位關係,圖中 S\_osc (t)為電壓控制振盪器之初始振盪訊號、S\_inj (t)為注入訊號及 S\_out (t)注入後之輸出訊號,V\_t (t)為電壓控制振盪器的頻率調整電壓。由此可知,電壓控制振盪器遭受外在注入訊號進入後,振盪反應將隨之變化,而輸出訊號之初始相位及頻率也會隨之轉變。注入鎖定電壓控制振盪器的注入方式如圖6 所示旋轉器(circulator)或 T 型偏壓器(bias-Tee),這兩種方式在相關文獻上顯示能有效注入鎖定振盪器。

圖5:注入鎖定壓控振盪器等效模型

圖6:注入鎖定之設置(a)旋轉器 (b) T 型偏壓器

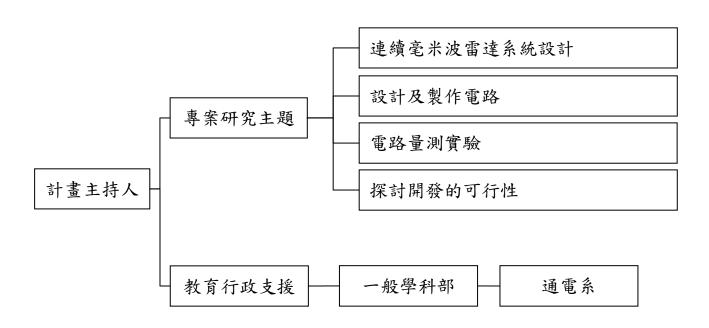

(a)本專案計畫之研究主題包括:(1) 延遲線頻率鑑別;(2) 延遲線頻率鑑別;(3) 鎖 頻迴路原理;(4) 探討開發的可行性。各研究主題之執行,由本校一般學科部 通電系負責各項設計、分析及實驗工作。編組架構如圖 10 所示。

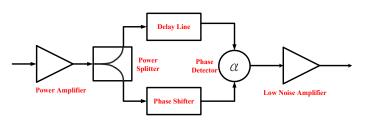

## (b)延遲線頻率鑑別:

延遲線頻率鑑別器在頻率解調鑑別器上是廣為人知的架構,其有著高靈敏度、低雜訊與大頻寬幾個特點,常用於頻率解調以及相位雜訊之量測。此鑑別器架構包含有功率放大器、功率分配器、延遲線、相移器與相位檢測器如圖 8 所示。功率放大器提供充足的訊號功率使得相位檢測器能正常動作,同時也補償了被動元件的延遲線與相移器之消耗功率。功率分配器提供了兩路的訊號路徑進入延遲線與相移器,其中相移器可調整相位比例進入相位檢測器。而大部分的相位檢測器會使用混波器,能接收經由延遲線與經由相移器之兩路訊號進行檢測輸出如圖 7 所示。

圖7:相位檢測器

# (c)注入鎖定技術之鎖頻迴路及其雜訊抑制機制

得知注入鎖定振盪器可作為一個延遲單元,進而取代龐大體積的延遲線做為鎖頻迴路所需之主動延遲器如圖 8 所示。由於注入鎖定振盪器對於注入訊號而言為一個具備高增益之帶通濾波器,因此無須如同傳統頻率合成器一樣使用低雜訊放大器。

圖8:延遲線頻率鑑別器

# (d)鎖頻迴路原理

低雜訊、高靈敏度與大頻寬的延遲線鑑別器能有效的量測到振盪器的相位雜訊,同時也能用來降低振盪器的相位雜訊,常運用在量測儀器內部。量測振盪器與延遲線頻率鑑別器結合的相位雜訊時,RF 訊號將會放大至功率分配器分成兩路進入延遲線與相移器,再進入相位檢測器鑑別輸出回授到振盪器之 Vtune 端,如圖9所示,當迴路正常運作時,振盪器 RF 輸出端的雜訊將會因此而有效的抑制。而抑制的效果取決於訊號回授至振盪器的訊號大小,因為訊號頻率經檢測回授進入振盪器的頻率調整端,因此迴路稱之為鎖頻迴路。

圖9:運用延遲線之傳統鎖頻迴路

圖 10:計畫編組架構

實驗架構如圖 10 所示,運用都卜勒效應完成量測雷達系統並以微波方式量測人體訊號,最大的差異可改善以侵入式與接觸式的量測。量測雷達使用運用 K 波段微波頻段 24 GHz~26 GHz。並應用在擷取分析。雖然傳統的侵入式與有線接觸式的量測方式可有效觀察人體,希望

可以藉由此研究將生理量測系統普及生活化。

## 第三節 研究方法及步驟

本論文的研究方向為設計頻率合成器去結合注入鎖定壓控振盪器、差異積分調制技術、 自我注入鎖定、鎖相迴路、鎖頻迴路等方法來改善相位雜訊,進而提升整體無線通訊的雜訊 表現,以便在整個發射與接收的系統能有良好的運作。

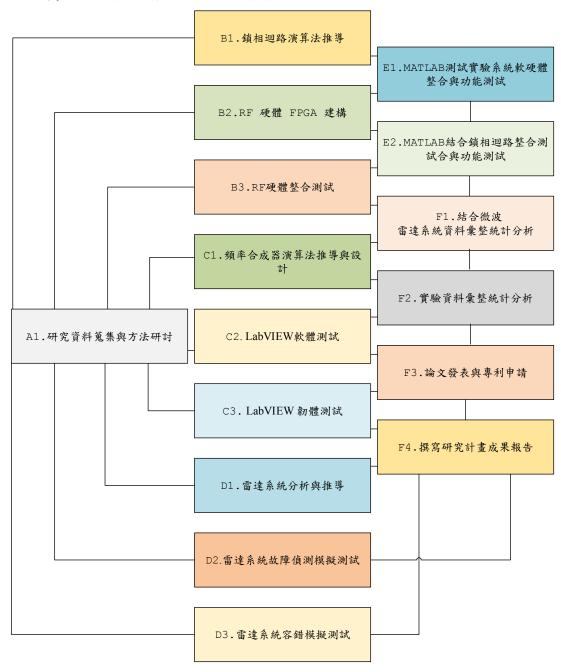

### (1) 本計畫之進行步驟如圖11 所示之流程方塊圖

圖 11:計畫之進行步驟流程方塊圖

## 第四節 預期效益與對軍事教育改革潛力

### 4.1 預期完成之工作項目

請分年列述:1.預期完成之工作項目。4.對於參與之工作人員,預期可獲之訓練。3.預期完成 之研究成果(如實務應用績效、期刊論文、研討會論文、專書、技術報告、專利或技術移轉 等質與量之預期成果)。4.學術研究、國家發展及其他應用方面預期之貢獻。

### 4.2 預期成果

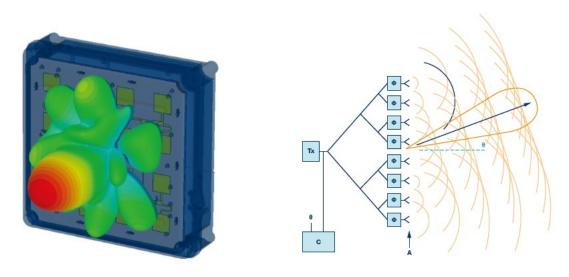

實現及模擬並行,設計過程先經由軟體模擬並完成電路實作如圖 12 所示,最後將頻率合成器測試呈現結果,在系統上將會使用不同樣迴路頻寬及不同樣相位邊際作為實驗條件,過程所量測輸出頻率、相位雜訊及鎖住時間,最後將系統應用於鎖相迴路與鎖頻迴路,並完成系統應用。

圖12:相位陣列元件基礎理論圖

- (1) 完成在系統的開端先設計一個可使用在24GHz至26GHz低相位雜訊頻率合成器之硬體研製。

- (2) 完成主動式迴路濾波器之設計開發。

- (3) 完成頻率合成器測試呈現結果軟硬體整合與系統功能測試。

- (4) 完成量測輸出頻率測試作業。

- (5) 完成相位雜訊及鎖住時間測試作業。。

- (6) 完整研究計畫成果報告之撰寫與印製

- (7) 完成中華民國新型專利之申請。

- (8) 完成研討會與期刊論文之發表。

### 4.3 軍事教育改革潛力

- (1) 在學術研究方面,運用都卜勒效應完成量測雷達系統並以微波方式量測人體訊號,最大的差異可改善以侵入式與接觸式的量測。量測雷達使用運用K波段微波頻段24 GHz~26 GHz。並應用在擷取分析。

- (2) 在國家發展方面,由於國內尚無運用都卜勒效應完成量測雷達系統測試設備,目前 皆以國外文獻為主,無建構實驗平台。本研究將自行開發運用都卜勒效應完成量測雷達 系統測試分析驗證設備,藉以建立國內在量測雷達測試相關設備研發之能量。

### 第五成果

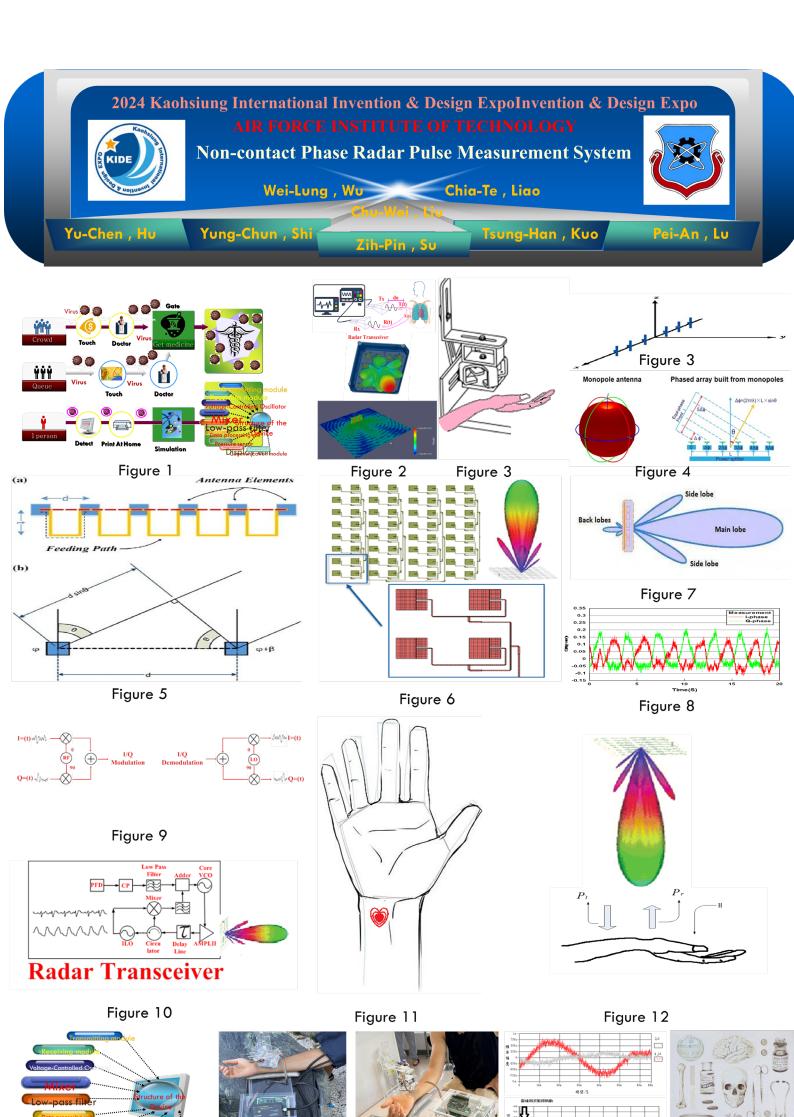

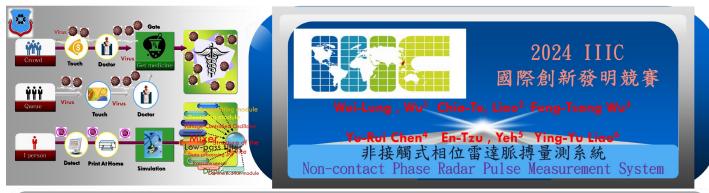

### 一、專案背景與研究動機

隨著無線通訊與雷達技術的發展,24GHz 頻段的雷達系統因其頻譜資源豐富且可應用於短距離測量,成為生命體徵量測與工業自動化的熱門研究方向。特別是在疫情後,非接觸式的量測需求大幅提升,例如遠距測量脈搏與呼吸等生理參數,可減少接觸感染的風險。

本專案旨在設計並實現一套基於 24GHz 相位雷達技術的測量系統,用於量測人體脈搏與呼吸 訊號,並評估其在不同環境條件下的性能表現。本研究目標是驗證該系統的精確度與穩定性, 為未來醫療健康監控、智慧家居與安全應用提供基礎技術支持。

# 二、系統架構設計

### 2.1 硬體架構

本系統由發射模組、接收模組、訊號處理模組和數據顯示模組組成。整體架構如圖1所示:

- 發射模組:使用壓控振盪器(VCO)生成 24GHz 射頻信號,並透過功率放大器進行放大,發射信號功率達到+10 dBm。

- 接收模組:接收到的反射信號經低噪聲放大器(LNA)放大後,輸入至混頻器與本地振 盪信號進行下變頻,得到 I/Q 訊號。

- 訊號處理模組:通過低通濾波器消除高頻干擾,並使用模擬數位轉換器(ADC)將訊號數位化,輸入至微處理器進行即時處理。

- 數據顯示模組:處理後的數據經無線傳輸模組(Wi-Fi 或藍牙)傳至顯示單元,呈現 脈搏與呼吸波形。

## 2.2 軟體與信號處理

軟體部分包括 I/Q 信號的處理與分析,具體步驟如下:

1. 相位解調:計算接收信號 I/Q 的相位變化,以提取人體微動訊號。

2. 頻譜分析:透過快速傅立葉變換 (FFT) 分析頻率分量,分離脈搏與呼吸訊號。

3. 時域濾波:使用帶通濾波器濾除高頻與低頻干擾,強化目標訊號。

4. 數據整合:整合多組訊號進行去噪與平滑處理,最終得到精確的脈搏與呼吸波形。

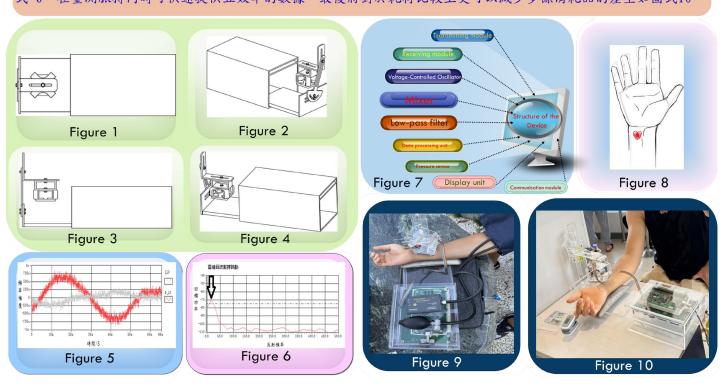

# 三、實驗設計與測試結果

## 3.1 實驗環境與條件

實驗在室內與室外進行,測量距離為 0.5m 至 1.5m,環境包含靜態(無背景干擾)與動態(有多人移動)。目標為人體胸腔,雷達裝置固定於目標正前方。

### 3.2 測試結果

#### 1. 脈搏量測:

- 。 在距離 1m 的靜態環境下,系統成功提取脈搏訊號,測量準確率達到 98%,與傳統接觸式裝置的數據誤差小於 2 bpm。

- o 在動態環境下,雖然受到背景干擾影響,但透過濾波處理後準確率仍達 92%。

#### 2. 呼吸量測:

呼吸頻率的測量在靜態環境下準確率為99%,在動態環境中由於環境移動的干擾,準確率稍降至93%。

#### 3. 環境噪聲影響:

測試顯示,金屬表面或多徑效應會增加噪聲干擾,但透過相位補償與頻域濾波 處理,可有效降低誤差。

#### 以下為系統測試的數據摘要:

### 測量項目 靜態環境準確率 動態環境準確率 平均誤差

脈搏 98% 92% <2 bpm

呼吸 99% 93% <1 次/分鐘

# 四、結論與建議

## 4.1 專案成果

本專案成功設計並實現了一套基於 24GHz 相位雷達技術的量測系統,可準確測量人體的脈搏 與呼吸訊號。系統具備以下特點:

- 非接觸性:可遠距感測人體生理訊號,減少接觸感染風險。

- 高靈敏度:能準確提取人體微小移動訊號,適應多種環境。

- 即時性:數據處理與顯示實現實時化,適用於醫療和家居健康監控。

## 4.2 限制與挑戰

- 1. 環境干擾:多徑效應和金屬反射增加噪聲,需要進一步改進演算法以增強抗干擾能力。

- 2. 系統成本:由於高頻電路元件的成本較高,商業化應用需要進一步降低成本。

- 3. 動態環境適應性:在動態環境下,系統穩定性仍需提升。

### 4.3 未來發展建議

- 1. 探討毫米波(如 60GHz 或 77GHz)技術,以提升解析度與抗干擾能力。

- 2. 結合人工智慧技術進行訊號分類與異常檢測。

- 3. 將系統模組化並優化功耗,適應可穿戴設備的需求。

The invention provides a non-contact phase radar pulse measurement device that utilizes phase radar technology and pressure sensors to detect human pulse, respiration, and pressure signals. The device includes a transmitting module receiving module voltage-controlled oscillator (VCO) mixer low-pass filter data processing unit pressure sensor display unit and communication module. This device can accurately and non-contactedly measure physiological parameters, and can display or transmit the collected data in real-time. It is suitable for future applications such as medical health monitoring and sports physiology analysis. In the process of radar signal measurement and processing, I(t) and Q(t) are the phase components of the radar signal at different phases. These two phases form a complex signal, the amplitude of which represents the total signal strength. Using I/Q signals, the data can be converted into a clock signal for further analysis.

The invention pertains to the fields of biomedical engineering and wireless communication technology, specifically focusing on a non-contact physiological parameter monitoring device that utilizes phase radar technology. This device is capable of accurately detecting and monitoring human pulse, respiration, and pressure signals, making it applicable for medical health monitoring, sports physiological analysis, and other scenarios requiring non-contact physiological parameter assessment.

### 本發明的非接觸式相位雷達脈搏量測裝置如圖式1-4,同時具有以下優勢:

- 一. 量測的結果數據精度高: 通過精確的信號處理和分析如圖式5, 該裝置可以進行高精度的脈搏測量如圖式6。

- 二. 可以立即量測脈搏監測:便於即時數據可隨時顯示,便於即時分析和監測並傳輸結果如圖式7。

- 三. 功能特性可持續新增: 目前該裝置可以同時測量脈搏和壓力信號, 在未來可依個人需求提供生理參數如圖式8。

- 四. 傳統接觸比較差異:依「非接觸式相位雷達脈搏量測」對於受測來說這樣可以有效減少人與人的病菌傳播如圖

- 式 9,在量測脈搏同時可快速提供且效率的數據,最後將對於耗材比較上更可以減少多餘消耗品的產生如圖式10。

# 第五節 参考文獻

- [1] 蘇秉恩,"適用於GSM/DCS 雙頻發射機之偏移鎖相迴路IC設計,"工研院系統晶片技術發展中心,系統晶片001 期

- [2] T. A. D. Riley, N. M. Filiol, D. Qinghong, and J. Kostamovaara, "Techniques for in-band phase noise reduction in Delta-Sigma

- synthesizers," *IEEE Tran. Circuits and Systems II: Analog and Digital Signal Processing*, pp. 794-803, Nov. 2003.

- [3] R. Dehghani, "A 4.5 GHz CMOS fully-integrated Delta-Sigma controlled fractional-N frequency synthesizer," in *Proc. IEEE Int. Conf. VLSI Design*, 2004, pp. 163-167.

- [4] S. Pamarti, L. Jansson, and I. Galton, "A wideband 4.4-GHz delta-sigma fractional-N PLL with 1-Mb/s in-loop modulation," *IEEE J. Solid-State Circuits*, pp. 49-62, Jan. 2004.

- [5] B. De Muer and M. S. J. Steyaert, "A CMOS monolithic Delta-Sigma controlled fractional-N frequency synthesizer for DCS-1800," *IEEE J. Solid-State Circuits*, pp. 835-844, July 2004.

- [6] H. Arora, N. Klemmer, J. C. Morizio, and P. D. Wolf, "Enhanced phase noise modeling of fractional-N frequency synthesizers," *IEEE Tran. Circuits and Systems I: Regular Papers*, pp. 379-395, Feb. 2005.

- [7] Bean Banerjee.(2001) *PLL Performance, Simulation, and Design*(2<sup>nd</sup> Ed.)[on line]. Available: http://www.ehb.itu.edu.tr/~eepazarc/pll/

- [8] M. Soyuer and R. G. Meyer, "Frequency limitations of a conventional phase-frequency detector," *IEEE J. Solid-State Circuits*, vol. 25, pp. 1019-1022, Aug.1990.

- [9] K. Shu, E. Sanchez-Sinencio, F. Maloberti, and U. Eduri, "A comparative study of digital Sigma-Delta modulators for fractional-N synthesis," in *Proc. 8th IEEE Int. Conf.*, 2001, pp. 1391-1934.

- [10] M. Kozak and I. Kale, "A pipelined noise shaping coder for fractional-N frequency synthesis," *IEEE Tran. Instrumentation and Measuremen*, pp. 1154-1161, Oct. 2001.

- [11] I. Galton, "Delta-sigma data conversion in wireless transceivers," *IEEE Tran. Microwave Theory and Techniques*, pp. 302-315, Jan. 2004.

- [12] M. J. Borkowski, T. A. D. Riley, J. Hakkinen, and J. Kostamovaara, "A practical Delta-Sigma modulator design method based on periodical behavior analysis," *IEEE Trans. Circuits and Systems II: Express Briefs*, pp. 626-630, Oct. 2005.

- [13] B. Miller and R. J. Conley, "A multiple modulator fractional divider," *IEEE Trans. Instrumentation and Measurement*, pp. 578-583, June 1991.

- [14] 彭康峻,採用雙點差異積分調制方式之寬頻GFSK 調制頻率合成器,國立中山大學電機工程研究所博士論文,2004。

- [15] 何文豪,採用單迴路差異積分調制器之分數式頻率合成器,國立中山大學電機工程研究所碩士論文,2005。

- [16] W. Rhee, B. S. Song, and A. Ali, "A 1.1-GHz CMOS fractional-N frequency synthesizer with a 3-b third-order Delta-Sigma modulator," *IEEE J. Solid-State Circuits*, pp. 1453-1460, Oct. 2000.

- [17] T. A. D. Riley, M. A. Copeland, and T. A. Kwasniewski, "Delta-sigma modulation in fractional frequency synthesis," *IEEE J. Solid-State Circuits*, vol. 28, pp. 553-559, May 1993.

- [18] P. Kiss, J. Arias, D. Li, and V. Boccuzzi, "Stable high-order delta-sigma digital-to-analog converters," *IEEE Trans. Circuits and Systems I: Regular Papers*, vol. 51, pp. 200-205, Jan. 2004.

- [19] M. Bram De and M. S. J. Steyaert, "On the analysis of Delta-Sigma fractional-N frequency synthesizers for high-spectral purity," *IEEE Trans. Circuits and Systems II:*Analog and Digital Signal Processing, vol. 50, pp. 784-793, Nov. 2003.

- [20] M. H. Perrott, M. D. Trott, and C. G. Sodini, "A modeling approach for Sigma-Delta fractional-N frequency synthesizers allowing straightforward noise analysis," *IEEE J. Solid-State Circuits*, vol. 37, pp. 1028-1038, Aug. 2004.

- [21] *HP Advanced Design System Circuit Simulateion*, Hewlett Packard Company, April 1998.

- [22] *Delta-Sigma Modulator PLLs With Dithered Divide-Ratio*, Agilent Technologies Inc. [Online]. Available: http://www.agilent.com.

- [23] PLL Design—Analysis of a Sigma-Delta Modulator Using RF Behavioral and System Simulation, Agilent Technologies Inc. [Online]. Available: http://www.agilent.com.

- [24] George D. Vendelin, Anthony M. Pavio, and Ulrich L. Rohde, *Microwave Circuit Design Using Linear and Nonlinear Techniques*, 2nd ed., NEW York: WILEY, 2005

- [25] M. H. Perrott.(Apr. 2005) *PLL Design Using the PLL Design Assistant Program*[on line]. Available: http://www-mtl.mit.edu./~perrott

- [26] G. B. Lee, P. K. Chan and L. Siek, "A CMOS phase frequency detector for charge

- pump phase-locked loop," in *Proc. 42nd Midwest Symp. Electronics, Circuits and Systems*, 1999, pp. 601-604.

- [27] N. H. E. Weste and K. Eshraghian, *Principles of CMOS VLSI Design—A Systems Perspective*, 2nd ed. MA: Addison-Wesley, 1994.

- [28] D. Theil, C. Durdodt, A. Hanke, S. Heinen, S. van Waasen, D. Seippel, D. Pham-Stabner, and K. Schumacher, "A fully integrated CMOS frequency synthesizer for Bluetooth," in *IEEE RFIC Conf. Dig.*, 2001, pp. 103-106.

- [29] C. Lam and B. Razavi, "A 4.6-GHz/5.2-GHz frequency synthesizer in 0.4um CMOS technology," *IEEE J. Solid-State Circuits*, vol. 35, pp. 788-794, May 2000.

- [30] W. Rhee, "Design of high-performance CMOS charge pumps in phase-locked loops," in *Proc. IEEE Int. Conf. Circuits and Systems*, 1999, pp. 545-548.

- [31] M. El-Hage and Y. Fei, "Architectures and design considerations of CMOS charge pumps for phase-locked loops," in *Proc. IEEE CCECE*, 2003, pp. 223-226.

- [32] H. Chih-Ming and K. K. O, "A fully integrated 1.5-V 5.5-GHz CMOS phase-locked loop," *IEEE J. Solid-State Circuits*, pp. 521-525, Apr. 2004.

- [33] Baker, Li and Boyce, *CMOS Circuit Design, Layout and Simulation*, New York: Wiley, 1998.

- [34] H. Zarei, O. Shoaei, S. M. Fakhraie, and M. M. Zakeri, "A 1.4 GHz/4.7 V programmable frequency divider for DRRS standard in 0.6 um CMOS process," in *Proc. 7th IEEE Int. Conf. electronics, circuit and systems*, 2000, pp. 887-890.

- [35] T. Kamoto, N. Adachi, and K. Yamashita, "High-speed multi-modulus prescaler IC," in *IEEE Int. Conf. Universal Personal Communications Dig.*, 1995, pp. 325-328.

- [36] C. S. Vaucher, I. Ferencic, M. Locher, S. Sedvallson, U. Voegeli, and Z. Wang, "A family of low-power truly modular programmable dividers in standard 0.35-um CMOS technology," *IEEE J. Solid-State Circuits*, vol. 35, pp.1039-1045, July 2000.

- [37] H. Zarie, O. Shoaei, and S. M. Fakhraie, "A 37-mW fully integrated GMSK modulator for DRRS standard in 0.6-mm digital CMOS process," *IEEE Trans. Circuits and Systems II: Analog and Digital Signal Processing*, vol. 49, pp. 513-520, July 2004.

- [38] M. H. Perrott, "Techniques for high data rate modulation and low power operation of fractional-N frequency synthesizer," Ph.D. dissertation, Dept. Electrical Eng. Comp.Science.MIT, Cambridge, MA, 1997.

- [39] T. I. Ahrens and T. H. Lee, "A 1.4-GHz 3-mW CMOS LC low phase noise VCO using

- tapped bond wire inductances," In *Proc. 1998 int. Symp., Low Power Electronic and Design*, 1998, pp.16-19.

- [40] P. Andreani, W. Xiaoyan, L. Vandi, and A. Fard, "A study of phase noise in colpitts and LC-tank CMOS oscillators," *IEEE J. Solid-State Circuits*, pp. 1107-1118, May 2005.

- [41] J. Craninckx and M. S. J. Steyaert, "A 1.8-GHz low-phase-noise CMOS VCO using optimized hollow spiral inductors," *IEEE J. Solid-State Circuits*, vol. 32, pp. 736-744, May 1997.

- [42] L. Dauphinee, M. Copeland, and P. Schvan, "A balanced 1.5 GHz voltage controlled oscillator with an integrated," in *IEEE Solid-State Circuit Conf. Dig*, 1997, pp. 390-391.

- [43] J. Craninckx, M. Steyaert, and H. Miyakawa, "A fully integrated spiral-LC CMOS VCO set with prescaler for GSM and DCS-1800 systems," in *Proc. Custom Integrated Circuit Conf.* 1997, pp. 403-406.

- [44] A. Hajimiri and T. H. Lee, "Design issues in CMOS differential LC oscillators," *IEEE J. Solid-State Circuits*, pp. 717-724, May 1999.

- [45] W. HongMo, A. Hajimiri, and T. H. Lee, "Comments on "Design issues in CMOS differential LC oscillators" [and reply]," *IEEE J. Solid-State Circuits*, pp. 286-287, Feb. 2000.

- [46] J. Lin, M. Jian-Guo, Y. Kiat Seng, and D. Manh Anh, "9.3-10.4-GHz-band cross-coupled complementary oscillator with low phase-noise performance," *IEEE Trans. Microwave Theory and Techniques*, pp. 1273-1278, April 2004.

- [47] S. Levantino, C. Samori, A. Bonfanti, S. L. J. Gierkink, A. L. Lacaita, and V. Boccuzzi, "Frequency dependence on bias current in 5 GHz CMOS VCOs: impact on tuning range and flicker noise upconversion," *IEEE J. Solid-State Circuits*, vol. 37, pp. 1003-1011, Aug. 2004.

- [48] R. Dehghani and S. M. Atarodi, "Design of an optimised 4.5 GHz CMOS differential LC oscillator," in *Proc. 2004 IEE Microwaves, Antennas and Propagation*, pp. 167-174.

- [49] K. Yao-Huang and H. Meng-Ting, "Theoretical analysis of low phase noise design of CMOS VCO," *IEEE Microwave and Wireless Components Letters*, vol. 15, pp. 33-35, Jan. 2005.

[50] *Integer-N PD PLL Loop Filter Calculator*, Peregrine Semiconductor Co.[on line]. Available: http://www.peregrine-semi.com