# 穿隧氧化層氮化技術對 SONOS 快閃記憶體之特性研究

吳家麟 $^{1*}$  高進興 $^2$  李志遠 $^3$  王哲釧 $^4$  廖健瑋 $^2$

1 國防大學理工學院國防科學研究所 <sup>2</sup>國防大學理工學院半導體實驗室 <sup>3</sup>國防大學理工學院電機電子工程系 <sup>4</sup>國防大學理工學院應用化學與材料科學系

## 摘 要

本研究藉由製作以一氧化二氮氧化法與一氧化氮退火法等兩種氮化技術所成長的穿隧氧化層並分析其影響 SONOS 快閃記憶體可靠度特性。結果發現雖然一氧化二氮氧化法 900℃高溫製程無法產生預期的電荷保存能力,並藉由電荷升壓法(charge pumping)驗證一氧化二氮氧化法之氮原子無法有效降低介面缺陷,但其耐電荷重複抹/寫的能力較佳,另一方面在高溫熱沉積成長穿隧氧化層再配合一氧化氮退火法的結果顯示,可同時提升元件漏電流特性、耐電荷重複抹/寫與資料保存能力,足以推證一氧化氮退火法之氮原子可經由擴散而堆積在介面上,改善氧化層的品質,並具有節省熱成本(thermal budget)的優點,本實驗結果可提供 SONOS 快閃記憶體可靠度提升之有效方法。

關鍵詞:SONOS,快閃記憶體,氮化,穿隧氧化層

# The Study of Characteristics on SONOS Flash Memory with Nitridation Tunnel Oxide

Jia-Lin Wu $^{1\ast},$  Chin-H<br/>sing Kao $^2$ , Chih-Yuan Lee $^3$ , Je-Chuang Wang<br/>  $^4$ , and Chien-Wei Liao $^2$

<sup>1</sup>School of Defense Science, Chung Cheng Institute of Technology, National Defense University

<sup>2</sup>Semiconductor Lab., Chung Cheng Institute of Technology, National Defense University

<sup>3</sup>Department of Electronic and Electrical Engineering, Chung Cheng Institute of Technology, National Defense University

<sup>4</sup>Department of Applied Chemistry and Material Engineering, Chung Cheng Institute of Technology, National Defense University

#### **ABSTRACT**

The reliability characteristics of SONOS (silicon-oxide-nitride-oxide-silicon) devices with different thin nitridation tunnel oxides are studied. Although the device with the tunnel oxynitride grown in N<sub>2</sub>O ambient at 900°C can not reach the expected retention, it still has better endurance capability. The interface states varified by charge pumping method can not be reduced effectively by incorporated nitrogen. On the other hand, the tunnel oxide fabricated by high-temperature oxide (HTO) with additional NO annealing treatment has better performance and modifies performance properties including leakage current, endurance, and retention. It is speculated that nitrogen could diffuse into and pile up at the SiO<sub>2</sub>/Si interface and thermal budget can be reduced. This study can provide a straightforward way of reliability improvement for future SONOS flash memory application. **Keywords:** SONOS, flash memory, nitridation, tunnel oxide.

文稿收件日期 99.2.12; 文稿修正後接受日期 99.5.13; \*通訊作者 Manuscript received February 12, 2010; revised May 13, 2010; \* Corresponding author

## 一、前 言

在全世界數位化潮流趨勢發展之下,對於數位資訊的儲存與流通在可攜式電子產品發展的重要性大幅提升,同時由於網路上資訊存取速度的提高,推動著多媒體影音資料在可攜式電子產品的運用與流動性廣泛且需求日益增大,因此具有容量大、速度快、省電且不怕震動的快閃記憶體(Flash Memory)乃成為可攜式電子產品的最佳儲存媒介[1]。

快閃記憶體是一種非揮發性記憶體,當電 源關閉後仍能保存資料的完整性,除此優點 外,快閃記憶體也擁有每個單位記憶體位元 (bit)低成本特點,使其能成功應用在不同的資 訊產品領域中,從個人電腦(PC)、手機、個人 數位助理(PDA),到數位相機、MP3 隨身聽、 視訊轉換器(STB)等。快閃記憶體具備高速讀 取、高密度、低價格的優勢,已成為記憶體市 場中僅次於動態隨機存取記憶體(Dynamic Random Access Memory, DRAM) 的第二大產 品,未來應可超越 DRAM,全球市場產值預 估將在 2012 年超過 700 億美元,英代爾公司 (Intel)宣稱其可能成為未來十餘年半導體製造 技術的帶動者及主要產品,目前我國半導體產 業更列為國家發展「兩兆雙星計畫」,未來十 年之內,仍屬國內產業重要投資項目之一。

快閃記憶體是結合三種非揮發性記憶體 E<sup>2</sup>PROM、ROM、DRAM 之優點發展出來的 產物,其商業產品首由東芝(Toshiba)工程師於 1984 年開發創造出來[2],在世代交替演進過 程中不斷地改良進步,目前快閃記憶體依據操 作原理與機制不同又可細分為二支,一是浮動 閘極元件(Floating Gate Device),另一是電荷 捕陷元件(Charge Trapping Device),後者以 SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) 記憶體為其主要發展的結構。目前快閃記憶體 中浮動閘極結構的元件技術成熟,仍然為市場 之主流產品,但此元件結構在國際半導體協會 所制定的技術藍圖(ITRS, International Technology Roadmap for Semiconductor)規劃 之發展趨勢下,在30奈米以下製程技術勢必 將面臨瓶頸。因浮動閘極記憶元件在元件尺寸 快速縮減趨勢下,由於電壓耦合效應及漏電流 因素考量,其垂直厚度有一定限制而不易縮 減,當然電荷就無法更快速進出穿隧氧化層, 而且高垂直厚度無法避免在高的電壓操作,自

然無法滿足省能的需求。

SONOS 主要的結構為擔任電壓控制角色 的複晶矽控制閘(S)、負責電荷屏障的阻障氧 化層(O)、作為電荷捕陷的氮化矽電荷捕捉層 (N)、負責電荷進出及保存的穿隧氧化層(O)及 矽基底(S)等五大部分,所以簡稱 SONOS。近 年來,電荷捕陷元件結構中 SONOS 記憶體採 用非導體之材料-氮化矽(Si<sub>3</sub>N<sub>4</sub>)當作電荷捕 捉層,使用分離式節點達成電荷捕陷及儲存, 使得元件等效垂直厚度與操作電壓得以降 低,達到省能之目的,以及降低記憶陣列與週 邊電路製程整合之困難度,加上記憶單元多元 化(Multi-bit / Multi-level per Cell)的技術,大幅 增加元件密度,故成為下一代非揮發性快閃記 憶體最有可能的候選者,以朝向單電子記憶體 (Single Electron Memory, SEM) 的最終目標 邁進[3]。

綜觀上述,雖然 SONOS 快閃記憶體既有 的優勢比傳統浮動閘極快閃記憶體要來的 多,但是目前市面上及產業界仍以浮動閘極快 閃記憶體為主流市場,原因是 SONOS 目前仍 有一些現存的問題,如寫入及抹除的速度較 慢、多次操作造成穿隧氧化層的退化,以及漏 電流造成資料保存的時間短少等,這些因素都 影響其元件的可靠度(reliability) [4],探究原 因,一方面我們希望對於電荷捕捉率要高,同 時電荷不易逃脫,在經過十年後,使電荷仍能 儲存相當數量可供讀取電壓判讀;但另一方面 又希望被儲存的電荷在寫入及抹除操作時,可 以迅速脫離,進而增加操作速率。所以,除了 電荷捕捉層氮化矽(Si<sub>3</sub>N<sub>4</sub>)結構優化之外,穿隧 氧化層及阻障氧化層的品質和位能障壁的高 低,都會影響快閃記憶體的性能,其中穿隧氧 化層所要扮演的角色是允許電荷藉由電場施 力而穿隧至電荷捕捉層或矽基底,且當電場消 失時,該層又可阻止電荷穿隧,其品質的好 壞,對快閃記憶體的性能舉足輕重。因此本研 究的目的,主要在提升穿隧氧化層之品質,經 由設計不同氮化技術的製程條件,並依據各種 特性量測結果作分析比較,從而歸納出 SONOS 穿隧氧化層製程的最佳條件,目的就 是要解決目前 SONOS 快閃記憶體面臨的上述 缺點,提供學術及產業界發展新一代快閃記憶 體的參考。

## 二、研究方法及理論

一般穿隧氧化層都以二氧化矽為主,而依現行製程的溫度所形成的二氧化矽多為非晶矽型,因此在高電場應力(High Field Stress)的操作下,會造成該層退化而使品質下降,因為記憶體的讀取、寫入與抹除主要都經過二氧化矽,經過多次被穿隧之後就會有穿破(Worn-Out)的情形發生,最後當導通路徑形成之後,就會發生崩潰的行為,記憶體的功用就喪失,因此以成長氦氧化矽薄膜來改善二氧化矽的品質也被廣泛的研究[5,6]。

早期閘極氧化層製程採用傳統乾式氧化,法(Dry Oxide),直接通入氧氣成長二氧化矽,其品質雖較濕式氧化法(Wet Oxide)佳,但在成長3 nm 左右的薄氧化層其製程技術與可靠異人層不易,膜厚均勻度與再現性控制較難成,且二氧化矽與矽基介面易造成矽懸強人(Dangling Band),後來專家學者提出改進方法為成長二氧化矽層時通氨氣(NH3)數的過過。但氫原子在氮化過程會與氮原子一質鍵,以及的問題。但氫原子在氮化過程會與氮原子一質鍵,當時不斷寫入或抹除之際,其電荷所攜帶的能類容易將 Si-H 鍵打斷使懸鍵重新產生,破壞薄膜品質。

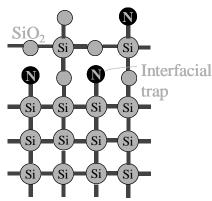

近來陸續由許多專家學者提出直接在爐管(Furnace)通入  $N_2O$  來成長氮氧化矽的穿隧氧化層來填補二氧化矽與矽基介面的矽懸鍵,如圖 1 所示,此一製程的氮原子會在氮氧化矽與矽基介面上堆積[7],然 Si-N 共價鍵結能大於 Si-H 鍵結能,如此可使得元件耐重覆抹寫能力更加提升,因通入  $N_2O$  其成長速率較為緩慢,可獲得較佳的厚度控制能力,而所成長的氮氧化矽其介電係數大於二氧化矽使其物理等效垂直厚度(Equivalent Oxide Thickness, EOT)更厚,元件更具電荷保存能力,如此一來可得到氧化層品質提升的好處。

但後續有文獻指出,此種方式成長的氮氧化矽因複晶矽之晶粒大小不一,氧化速率不均勻影響,容易有粗造界面產生,而不均勻度(Non-Uniformities)和氮的成分多寡有決定性關係[8]。一直到有文獻提出利用二次退火氧化法可改善上述情形,得到較低漏電流,氧化層品質可大幅提升[9]。

圖 1. 氮原子填補二氧化矽與矽基介面矽懸鍵示意 圖。

綜整而言,目前有兩種氮化技術成長氮氧 化矽,第一種為先成長二氧化矽,然後以快速 熱處理(RTP, Rapid Thermal Processing)方式, 通入含氮氣體同時進行退火。此方法所形成的 氮氧化矽,在介面的含氮量雖然較高[10],但 是對於厚度控制及均勻度(Uniformity)仍須注 意;第二種方式直接在高溫下通入含氮氣體, 而形成氮氧化矽,雖然均匀度較佳,但是在介 面的氮含量相對於第一種方法卻降低數倍 [11]。以上氮化技術已部份運用在傳統的浮動 閘極記憶體,但是氮氧化矽製程條件對於 SONOS 快閃記憶體可靠度的影響還未被詳細 的報導,故本實驗將研究一氧化二氮氧化法與 一氧化氮退火法等兩種氮化技術所成長的高 品質穿隧氧化層,並分別探討對 SONOS 快閃 記憶體特性的影響,因為氮化技術亦具有精確 厚度控制與無氫原子參雜的優點,依據文獻研 究氮原子的分佈情形, 氮原子將會擴散進入二 氧化矽並堆積在二氧化矽與矽的介面以降低 介面狀態(interface states)[8],並發現具有較高 氮原子的成分將會改善其可靠度,因此利用氮 化技術所形成的穿隧氧化層比傳統乾式氧化 層更適合未來 SONOS 快閃記憶體的發展與運 用。

本實驗之電性量測在電容-電壓特性方面,以準靜態電壓-電容量測系統(Keithley 590 C-V Analyzer)進行量測;在電流-電壓之相關性能表現、漏電流及可靠度分析等項目評估方面,則以 Agilent 4156C 高精準半導體參數分析儀、Agilent 81104A 脈衝/碼型產生器及Agilent E5250A 多通道切換矩陣控制器作為主要量測儀器平台,並利用電荷升壓法(charge pumping)量測介面狀態(interface states),以探

討不同製程條件之穿隧氧化層特性影響。

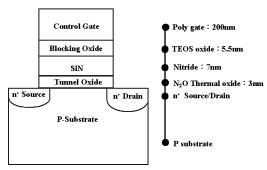

圖 2. SONOS 快閃記憶體結構示意圖。

## 三、薄膜沈積製程與步驟

## 3.1 一氧化二氮氧化法 (N₂O Oxidation)

具有 ONO (oxide-nitride-oxide) 結構的 SONOS 快閃記憶體元件如圖 2 所示,所有試 片的製作皆使用 p 型矽(100)晶圓,在完成區域氧化隔離 (Local Oxidation of Silicon, LOCOS)之後,除了閘極氧化層被 ONO 介電層所取代之外,所有製程都遵循傳統的標準負通道金屬氧化物半導體 (N-channel Metal Oxide Semiconductor, NMOS)製程步驟。

首先成長最重要的穿隧氧化層,本實驗對 於穿隧氧化層的製作,一共規劃了四個條件, 其中直接通以一氧化二氮氧化法(N<sub>2</sub>O Oxidation)製程溫度條件,分為 800°C 及 900°C 兩種。第三、四個條件為乾式氧氣氧化法(Dry O₂ Oxidation),溫度亦為 800°C 及 900°C 兩種。 所謂直接通一氧化二氮氧化法,係以  $N_2O/N_2=1/1$  的製程條件成長氮氧化矽,其中 NoO 與 No 每分鐘均通入各 1 公升的氣體流量 (slm, Standard Liter per Minute), 分別在 800°C 以及900℃環境下,與矽基底反應並成長氮氧 化矽(SiOxNv),因為在高溫下薄膜成長的速度 較快。因此設定溫度為800與900℃的氧化時 間,分別為28分鐘及8分鐘兩種,預期厚度 成長3奈米,並探討相關特性差異量比較;而 800°C 乾式氧氣氧化法是在溫度 800°C,直接 通乾氧 5 分 30 秒,900°C 乾式氧氣氧化法是 在溫度900℃,直接通乾氧3分鐘,預期成長 厚度是3条米,以上四種試片在完成後皆通入 7 slm 的 N<sub>2</sub> 氣體執行回火 15 分鐘,實際厚度 則是經過微幅調整垂直爐管的氧化時間以及

利用控片取得厚度的數據,最後利用橢圓測厚儀(Ellipsomter)的多點量測方式確認皆為 3 奈 米,相關製程規劃如表 1 所示。

表 1. 一氧化二氮氧化法四組試片製程條件規劃

| Process steps and conditions<br>for test chips |                                            | Wafer Splits |          |          |          |

|------------------------------------------------|--------------------------------------------|--------------|----------|----------|----------|

| Process steps                                  | Process conditions                         | I            | п        | ш        | IV       |

| Tunnel oxide<br>growth                         | N <sub>2</sub> O/N <sub>2</sub> 1slm 800°C | $\vee$       | Г        |          |          |

|                                                | N <sub>2</sub> O/N <sub>2</sub> 1slm 900°C |              | $\vee$   |          |          |

|                                                | O <sub>2</sub> 1slm 800°C                  |              |          | >        |          |

|                                                | O <sub>2</sub> 1slm 900°C                  |              |          |          | $\vee$   |

| Nitride<br>deposition                          | Modified nitride                           | <b>v</b>     | <b>V</b> | <b>v</b> | V        |

| Blocking<br>oxide<br>deposition                | 695℃ TEOS                                  | ~            | <b>v</b> | >        | <b>/</b> |

| Poly gate<br>deposition                        | PH <sub>3</sub> -doped poly                | ~            | <b>~</b> | <b>v</b> | <b>V</b> |

| P <sup>+</sup> well<br>implant                 | BF <sub>2</sub>                            | ~            | <b>v</b> | ٧        | <b>v</b> |

| Passivation                                    | 550nm TEOS                                 | $\vee$       | V        | V        | $\vee$   |

| Contact &<br>Metal                             | Al-Si-Cu sputtering                        | <b>v</b>     | <b>v</b> | V        | V        |

接著在 780°C 環境下利用低壓化學氣相 沉積(LPCVD)製作厚度為 7 nm 的改良式 (modified)氮化矽層,此種電荷捕捉層的沉積 過程是改變 SiH<sub>2</sub>Cl<sub>2</sub>/NH<sub>3</sub> 的比例從 2.07 到 0.1, 结果形成底部矽原子較多而頂部氮原子 較多的能階變化組合而成的薄膜,因為矽原子 較多可以增加捕陷電荷的數量,而氮原子較多 可以增加捕陷的能階深度,並已經在過去文獻 中獲得證明可以提高捕陷效率與可靠度 [12],故本實驗所有試片皆以改良式氮化矽層 製作,再覆蓋一層厚度為 5.5 nm 由四乙基正 矽酸鹽 (Tetraethyl Orthosilicate, TEOS) 在 695℃沉積而成的阻障氧化層,最後再依序完 成多晶矽閘極、源極/汲極(S/D)、佈植、金屬 接觸與量測接點等製作,測試元件選擇通道長 度 0.8 μm、寬度 5 μm 為主要測試結構,其 ONO 結構的等效厚度(EOT)可由高頻電容-電 壓(C-V)量測來獲得。

#### 3.2 一氧化氮退火法 (NO annealing)

爲了探討在半導體廠成長二氧化矽常使用的製程方式,故與力晶半導體股份有限公司合作,選擇具有 NAND 結構的 SONOS 快閃記憶體,所有製程皆在力晶公司完成,試片是由 p 型矽基底並加入淺溝渠隔離技術(STI)區

隔元件,除了閘極氧化層是由 ONO 介電層所 取代之外,全程以標準 NMOS 製程來製作。

本研究規劃三種實驗條件,三組試片的穿 隧氧化層皆有相同厚度為 2.5 nm, 以用來比較 SONOS 的特性,首先兩組高溫氧化法 (High-Temperature Oxide, HTO)元件的穿隧氧 化層是利用低壓化學氣相沉積(LPCVD) 在 780°C 環境下製作,其中一組再經過額外 950°C、35 秒的一氧化氮(NO)退火處理,另一 組則無 NO 退火處理以作為比較對照組;第三 組即時蒸氣成長氧化法(In-Situ Steam Generated oxide, ISSG)試片的穿隧氧化層是在 15%氫氣含量環境下以 950°C、16 秒製作完 成;三組試片接著利用低壓化學氣相沉積 (LPCVD) 在 700°C (SiH<sub>2</sub>Cl<sub>2</sub>/NH<sub>3</sub>=1/10)環境下 製作厚度為 6 nm 的均匀氮化矽層,再覆蓋一 層厚度為 6.5 nm 由高溫氧化法(HTO)在 780℃ 沉積而成的阻障氧化層,最後依序完成多晶砂 閘極、源極/汲極(S/D)、佈植、金屬接觸與量 測接點等製作,測試元件選擇通道長度 0.5 μm、寬度 0.13 μm 為主要測試結構,其 ONO 結構的等效厚度(EOT)可由高頻 C-V 量測來獲 得。

## 四、實驗結果與討論

## 4.1 一氧化二氮氧化法 (N<sub>2</sub>O Oxidation)

本研究規劃四種實驗條件,分別是  $N_2O$  800°C、 $N_2O$  900°C 及 Dry 800°C、Dry 900°C 等四種 SONOS 快閃記憶體來作比較,在電容-電壓特性方面,選取面積為  $2.50\times10^{-3}$  cm² (500  $\mu$ m  $\times$  500  $\mu$ m)大小的 MOSC;在電流-電壓之相關性能表現、漏電流及可靠度分析等項目評估方面,選取 SONOS 記憶元件通道長度  $0.8~\mu$ m、寬度為  $5~\mu$ m 為主要測試結構,其量 測結果分述如后:

#### 4.1.1 C-V 特性

SONOS 結構之記憶元件之 C-V 特性量測,四組測試晶片  $N_2O$  800°C、 $N_2O$  900°C 及 Dry 800°C、Dry 900°C 其 C-V 特性曲線經由量測後換算其 ONO 層之等效厚度均約為 12 nm,驗證製程相關參數、條件控制得宜;其膜厚均勻度良好,可供後續電性量測分析比較。

#### 4.1.2 漏電流特性

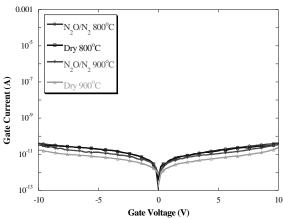

穿隧氧化層品質之好壞,除了以物理與材 料特性探討之外,可由一些基本電性量測來判 斷。首先對元件實施閘極漏電流測試,驗證穿 隧氧化層薄膜,元件採通道長 0.8 μm、寬 5 μm,其方法為將元件兩端源極與汲極浮接 (Floating)且將矽基本體接地(Ground)並於閘 極分別以 0 到 ±10 V 的偏壓範圍掃描閘極漏 電流,由量測結果的圖3研判,在閘極電壓為 -5V 時為例,以 Dry 900°C 成長之二氧化矽漏 電流最低(7.2×10<sup>-12</sup> 安培), 其次是 N<sub>2</sub>O 900°C (1.3×10<sup>-11</sup> 安培),顯示高溫成長環境可以降低 缺陷的形成,而 N<sub>2</sub>O 800°C (2×10<sup>-11</sup>安培)與 Dry 800°C (2×10<sup>-11</sup> 安培)漏電流相同,研判皆因內 部缺陷與介面缺陷可能較多,使得電荷經由缺 陷輔助穿隧機制(Trap-Assisted Tunneling, TAT)流動機率大增,因此造成較大的閘極漏電 流,可知以高溫成長之穿隧氧化層其品質獲得 提昇,且溫度 900°C 優於 800°C,其中 N<sub>2</sub>O 900℃初步研判因為氮原子無法完全堆積在介 面上,反而一部份散佈在薄膜之中,故並未明 顯看到氮原子在穿隧氧化層氮化過程中減少 介面缺陷所產生預期較佳的漏電流特性,而 Dry 900°C 反而具有較佳的氧化層品質,亦可 由 4.1.6 節介面分析結果獲得驗證。

#### 4.1.3 寫入與抹除特性

在記憶元件發展趨勢不可避免需使用熱 載子注入(Channel Hot Electron Injection, CHEI)來發展高密度、高效能之快閃記憶體, 本實驗希望藉由熱載子對穿隧氧化層之影 響,探討氧化層之優劣,供製程研發參考。因 此實驗以通道熱電子做為電荷寫入機制探 討;同時利用能帶對能帶間穿隧產生的熱電洞 注入(Band to Band Hot Hole Injection, BBHHI) 來達到電性中和。因通道熱電子與能帶對能帶 間穿隧產生的熱電洞其操作機制對薄氧化層 破壞力比用 F-N 穿隧機制大且考量通道熱電 子寫入速度比 F-N 穿隧機制快,因此選定了 元件的寫入操作電壓為 $V_g = V_d = 8V$ 可得相 對最大的操作窗口,操作時間設定為1毫秒; 而選用  $V_0 = -5 \text{ V}$ ,  $V_d = +8 \text{ V}$  作為元件抹除操 作電壓,操作時間設定為100毫秒。

分別將四組不同條件成長之記憶元件以相同操作機制進行寫入/抹除操作,由圖 4 可得四組測試元件其操作窗口差別不大,均大約

為 3.8 V 左右,其原因分析係四組測試元件其電荷捕捉層均採改良式氮化矽(Modify Nitride)結構,因此電荷捕陷能階位置與數量大都相同,故操作窗口變化不大。然而  $N_2O$   $900^{\circ}$  C 在 10 ns 到 200 ns 之間展示出較快的寫入速度(8 V/ms 的斜率較陡,其他三組皆約為 6.4 V/ms),研判是 Dry  $800^{\circ}$  C 與  $N_2O$   $800^{\circ}$  C 具有較多的介面捕陷電荷,造成矽基底與二氧化矽之間的能障較高,因而在一開始降低了寫入速度,但此效應隨著寫入時間的增加而逐漸減緩 [13],而 Dry  $900^{\circ}$  C 因為無氮原子的參雜,缺陷輔助穿隧效應較不明顯。

圖 3. 一氧化二氮氧化法四组試片漏電流特性。

圖 4. 一氧化二氮氧化法寫入/抹除速度與操作窗口。

#### 4.1.4 重複讀寫特性

SONOS 之另一項優點為可以透過電性方式來達到資料的更新,換言之,當電荷存入氮化矽之電荷捕捉層,有可能因資料更新會將電荷抹除或再度寫入;每執行一次寫入及抹除動

作稱之為一個循環。但氧化層經過多次寫入/ 抹除循環操作會使元件性能退化,因此穿隧氧 化層耐重複寫入/抹除能力另一項評估元件可 靠度的方法。因此在元件耐久性測試上,其電 性量測環境設定需參照實際產品之操作條件 規範,考量操作速度與窗口,以圖 4 寫入/抹 除之量測結果為基礎,規劃通道熱電子寫入其 條之量測結果為基礎,規劃通道熱電子寫入其 操作偏壓設定維持不變,而寫入時間為 1 ms; 又氮化矽具有較深層捕陷能階,電荷一旦被捕 陷後較難逃逸出來,因此電荷抹除機制方面採 能帶對能帶間穿隧產生的熱電洞將其操作偏 壓與抹除時間設定維持 100 ms。

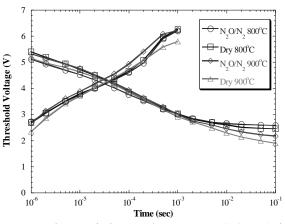

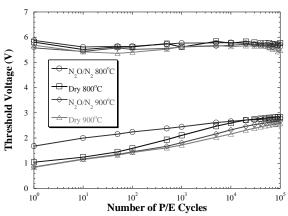

從圖 5 量測結果可發現經過 10 萬次重覆 寓入/抹除之後,其耐久特性表現在臨界電壓 是高位準 (寫入狀態) 時的量測結果變化相似 (約在 5.5-5.8 V),但是在低位準 (抹除狀態) 有少數電荷仍然留在氮化矽層,因為愈來愈多電荷在深層能階被捕陷,使得電子與電洞錯位 (mismatch)而造成愈來愈不易抹除(上升到約 2.5-2.8 V) [14];綜觀四組在經過 10 萬次重覆 寫入/抹除之後,仍然能夠維持足夠的操作窗口(約為 3 V)。

圖 5. 一氧化二氮氧化法 10 萬次重複讀寫特性。

#### 4.1.5 資料保存性

由於實際記憶元件產品不太可能實施 10 年電荷保存持久性測試,因此參考文獻相關量 測方法,時間參數設定基準以1萬秒為測試週 期,透過不斷的讀取臨界電壓變化來量測其電 荷流失的情況;其後再採能帶對能帶間穿隧產 生的熱電洞將電荷抹除並測試 1 萬秒之臨界 電壓變化。最後將寫入狀態、抹除狀態的電荷 保存能力曲線作圖並外插至 10 年,所得之臨 界電壓變化量來判定電荷保存能力。

由圖 6 量測結果可得知,四組測試元件經 一次寫入/抹除的操作後雖然 Dry 900℃ 操作 窗口最大約 4.3 V, 其次是 N<sub>2</sub>O 900°C 約 4.1 V, Dry 800°C 約 3.8 V, 而 N<sub>2</sub>O 800°C 操作窗 口最小約 3.6 V,但經過 1 萬秒後的電荷持久 性量測,當時間軸取 Log Scale 時發現 2000 秒後其臨界電壓似乎呈一線性變化,因此採用 2000 秒至 1 萬秒的資料求其外插至 10 年操作 窗口,其外差 10 年後之操作窗口為 Dry 900℃  $(2.5 \text{ V}) > N_2O 900^{\circ}C (1.6 \text{ V}) > Dry 800^{\circ}C (1.1 \text{ V})$ >N<sub>2</sub>O 800°C (0.2 V);得知 900°C 高溫成長之 二氧化矽具有較優之電荷保存能力,10 年之 後仍保有較大操作窗口約 2.5 V,但是仔細觀 察 Dry 900°C 與 N<sub>2</sub>O 900°C 自 1 萬秒後的電 荷流失率(斜率)較為接近,其分析原因可能 其高溫成長之二氧化矽與氮氧化矽結構之穿 隧氧化層皆具有較佳品質,降低電荷穿隧的效 應,所以電荷經過長時間仍具較大操作窗口供 做資料判讀。

本實驗更重要的是觀察重複讀寫後的資 料保存性,在經過量測 10 萬次重複寫入/抹除 的循環操作之極漏電流特性後,再量測此四組 測試件的電荷保存能力,由於低位準臨界電壓 變化率很小,所以單就高位準臨界電壓的斜率 來做比較,其量測結果如圖 7 所示,將 2000 秒至1萬秒區間所量測到的數據外差至10年 後,高位準臨界電壓變化率由低到高分別為 Dry  $900^{\circ}\text{C} < \text{N}_2\text{O} 900^{\circ}\text{C} < \text{Dry } 800^{\circ}\text{C} < \text{N}_2\text{O}$ 800°C, 其中 Dry 900°C 的資料保存力仍然最 好,而 Dry 900°C 與 N<sub>2</sub>O 900°C 自 1 萬秒後 的電荷流失率(斜率)較為接近,N<sub>2</sub>O 800℃ 的性能最差,由於低位準臨界電壓經過重複讀 寫後被提高(如圖5所示),導致10年後的操 作窗口皆大幅下降,但 Dry 900℃ 在 10 年後 仍有大於 1 V 的操作窗口; 另將量測結果與圖 6 比較後可知, Dry 900°C 在實施重複讀寫後 10 年的高位準臨界電壓值比實施單次寫入/抹 除後 10 年的電壓值下降較多,反而  $N_2O$   $900^{\circ}C$ 無明顯變化,顯示 Dry 900℃ 受到重複讀寫後 的穿隧氧化層仍會稍微退化,研判 N<sub>2</sub>O 900°C 的電荷流失較 Dry 900℃ 為快的原因,可能是 塊體(bulk)內參雜氮原子主導所造成,但在重 複讀寫後 N<sub>2</sub>O 900℃ 的高位準臨界電壓值與 單次讀寫的相仿(約為3 V),顯示介面缺陷上 由於氮原子的填入發揮了作用,提高資料的耐 久性與保存性。

圖 6. 一氧化二氮氧化法室温資料保存特性。

圖 7. 一氧化二氮氧化法 10 萬次重複讀寫後 室溫資料保存特性。

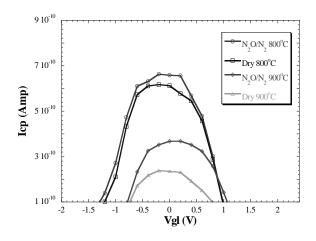

#### 4.1.6 介面分析

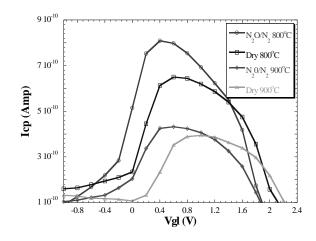

針對實驗試片實施電荷升壓法(charge pumping)量測介面狀態,使用頻率 $1\,\mathrm{MHz}$ ,閘極電壓的高低狀態差設為 $2\,\mathrm{V}$ ,只要施加的電壓超過該元件平帶及臨界電壓範圍內,就可量測到電荷升壓電流( $I_{\mathrm{CP}}$ ),並依電流大小可分析介面狀態(interface state)分佈的多寡,相關證別結果如圖 8,由  $I_{\mathrm{CP}}$ 電流的大小可以驗證試片介面缺陷,我們大致可以發現  $I_{\mathrm{Cp}}$ 電流的大小呈現兩個族群,分別為  $N_2\mathrm{O}$  800°C、Dry 800°C 與  $N_2\mathrm{O}$  900°C、Dry 900°C,其中 Dry 900°C 介面缺陷最少,由此可知,愈高溫度愈長的穿隧氧化層確有較佳的品質,因為溫度愈高則動能越大,導致晶粒(Grain)排列就越整齊,晶粒就越緻密,缺陷就會越少。

為進一步探討記憶元件在不同測試條件 下可靠度的性能表現,驗證穿隧氧化層之優 劣,也同樣將四組測試元件經過 10 萬次循環

抹/寫後再量測其介面缺陷變化情形,以佐證 氧化層品質優劣,其量測結果如圖9所示,可 以發現四組測試元件介面缺陷的優劣順序還 是與未經過10萬次循環抹/寫前的結果相同, 但是明顯看到四組試片的 Icp 值都有所增加, Dry 900°C 由 2.4×10<sup>-10</sup> 安培上升至 4×10<sup>-10</sup> 安 培, N<sub>2</sub>O 900°C 由 3.7×10<sup>-10</sup> 安培上升至 4.3× 10<sup>-10</sup> 安培, Dry 800°C 由 6.2×10<sup>-10</sup> 安培上升至 6.5×10<sup>-10</sup> 安培, N<sub>2</sub>O 800°C 由 6.7×10<sup>-10</sup> 安培上 升至 8.2×10<sup>-10</sup> 安培,表示經過 10 萬次重複寫 入/抹除之後確實會對穿隧氧化層造成一定的 傷害,進而對元件的特性造成一定的影響。而 以相同成長溫度的試片來加以比較,通入 N<sub>2</sub>O/N<sub>2</sub> 所成長的試片都有比乾式氧化法所成 長的試片有著更多的介面缺陷,似乎氮原子並 沒有如預期中的對介面缺陷發揮填補的作 用,同樣的結果也出現在未經過 10 萬次循環 抹/寫的 Charge Pumping 結果中。但是我們發 現在經過重複讀寫之後 Dry 900°C 的介面缺陷 增加量較多,最後幾乎與 N₂O 900°C 一樣,研 判在二氧化矽與矽基底介面上的氮原子具有 抵抗重複讀寫的特性,也印證在重複讀寫後資 料保存性所觀察到的結果。

因此我們可以推論在越高溫所成長的二氧化矽品質越佳,但以  $N_2O$  900 °C 所成長的穿隧氧化層,其氮原子雖然無法確實的有效降低介面狀態,故在漏電流與資複讀寫後的性程度卻比 Dry 900°C 較小,研判與氮原子檢體人工是獨立 () 是經過一種,因為在高溫環境的內容。 () 是經過一種,因為在高溫環境的內容。 () 是與人 () 是, (

#### 4.2 一氧化氮退火法 (NO annealing)

本研究規劃三種實驗條件,分別是即時蒸氣成長氧化法(In-Situ Steam Generated oxide, ISSG)、高溫氧化法(High-Temperature Oxide, HTO)以及具有 NO 退火處理的高溫氧化法(HTO(NO\*))等三種 NAND 結構的 SONOS 快閃記憶體來作比較,在電容-電壓特性方面,

選取面積為  $5.76 \times 10^4 \, \text{cm}^2$  大小的 MOSC; 在電流-電壓之相關性能表現、漏電流及可靠度分析等項目評估方面,選取 SONOS 記憶元件通道長度  $0.5 \, \mu \text{m}$ 、寬度為  $0.13 \, \mu \text{m}$  為主要測試結構,其量測結果分述如后:

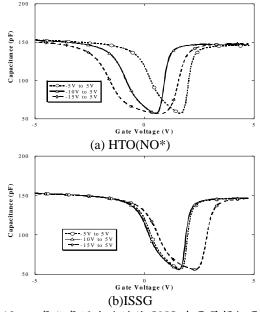

#### 4.2.1 C-V 特性

選取面積為 5.76 × 10<sup>-4</sup> cm<sup>2</sup> 大小且具有 SONOS 結構 MOSC 進行 C-V 特性量測,三組 測試晶片 ISSG、HTO 及 HTO(NO\*)其 C-V 特性曲線經由量測後換算其 ONO 層之等效厚度 均約為 13.4 nm,藉以驗證製程相關參數控制 得宜與膜厚均勻度良好,可供後續電性量測分析比較。

圖 8. 一氧化二氮氧化法電荷升壓特性。

圖 9. 一氧化二氮氧化法 10 萬次重複讀寫後電荷 升壓特性。

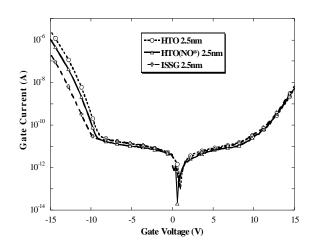

#### 4.2.2 漏電流特性

圖 10 顯示所有試件的漏電流曲線,在閘

極電壓為-5V 時為例,它證明了 HTO(NO\*)的直接穿隧漏電流(1×10<sup>-11</sup> 安培)稍小於其它二組試件(1.3×10<sup>-11</sup> 安培),顯示在一氧化氮退火的處理中氮原子降低了介面缺陷的形成;但是負閘極電壓 F-N (Fowler-Nordheim)穿隧發生時轉折向上較 ISSG 提早,這是因為介面上氮原子的參與降低了介面缺陷(interface state),有助於降低直接穿隧漏電流,然而整體二氧化矽內氮原子的少量增加卻造成較高的缺陷密度而有助於輔助穿隧漏電流(TAT)所造成上述的現象。

圖 10. 一氧化氮退火法漏電流特性。

#### 4.2.3 寫入與抹除特性

由於試片的穿隧氧化層厚度為較薄的 2.5 nm,加上 NAND 結構多以 FN 穿隧來達成寫 入電荷,同時 FN 穿隧較不會造成穿隧氧化層 的嚴重損傷,故本實驗希望藉由 FN 穿隧機制 對穿隧氧化層之影響,來探討氧化層之優劣, 以供製程研發參考。因此選定了元件的寫入操 作電壓為 Vg = 14 V 可得相對最大的操作窗 口,操作時間設定為 100 毫秒;而選用 Vg = -12 V 作為元件抹除操作電壓,操作時間設定為 500 毫秒。寫入與抹除的特性如圖 11 所示, HTO 與 HTO(NO\*)試片擁有比 ISSG 較大的操 作窗口,其中 HTO 展現較快的 FN 抹除速度, 是由於其較多的介面缺陷(interface state)有助 於輔助穿隧的電子抹除;另外針對 ISSG 較差 的抹除能力,我們設計了 C-V 掃描的實驗, 發現當施加負閘極偏壓時,HTO(NO\*)藉由來 自矽基底注入的電洞來完成 FN 穿隧抹除,造 成 C-V 曲線向左平移,如圖 12(a)所示,但是 發現 ISSG 的 C-V 曲線卻向右平移,顯示肇因 於閘極電子的提早注入,如圖 12(b)所示,因 此 ISSG 無法執行正常的抹除工作。

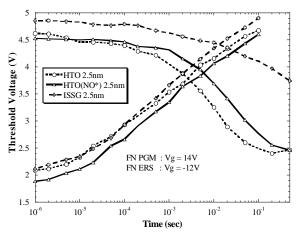

#### 4.2.4 重複讀寫特性

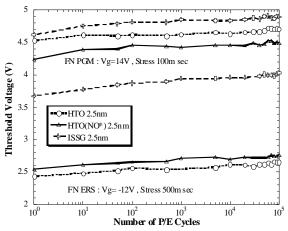

以寫入/抹除之量測結果為基礎,規劃FN 穿隧寫入與抹除其操作偏壓與時間設定維持 不變,從圖13結果可發現經過10萬次重覆寫 入/抹除之後,HTO與HTO(NO\*)試片擁有比 ISSG較大的操作窗口,是因為ISSG較差的抹 除特性造成在低位準(抹除狀態)具有高的臨 界電壓所導致的結果。

圖 11. 一氧化氮退火法寫入/抹除速度與操作窗口。

圖 12. 一氧化氮退火法試片 ONO 介電層掃描電容 -電壓特性: (a)HTO(NO\*); (b)ISSG。

圖 13. 一氧化氮退火法 10 萬次重複讀寫特性。

#### 4.2.5 資料保存性

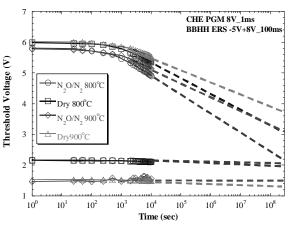

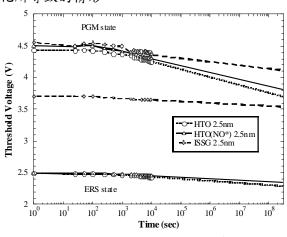

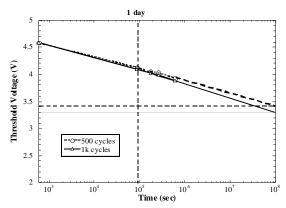

在室溫之下單次讀寫的資料保存特性由 圖 14 量測結果可得知,三組測試元件在低位 準臨界電壓變化率無明顯變化,但在高位準臨 界電壓的斜率就相當不同,雖然 ISSG 的臨界 電壓變化量小於 HTO,但因為其具有較高的 低位準臨界電壓(ISSG 不易抹除),操作窗口 相對較小;採用 2000 秒至 1 萬秒的資料求其 外插至 10 年操作窗口,其外差 10 年後 HTO(NO\*)與 HTO 操作窗口最大約 1.4 V, ISSG 操作窗口最小約 0.6 V,至此並未看出一 氧化氮退火的明顯效果;本實驗更重要的是觀 察重複讀寫後的資料保存性,在經過量測 10 萬次重複寫入/抹除的循環操作之後,再量測 此三組測試件的電荷保存能力,資料保存性 (retention)的測試結果如圖 15 所示,外插至 10 年後 HTO(NO\*)的操作窗口最大,亦即直接穿 隧流失的電荷量較少,而 HTO 的電荷流失量 最多,研判是介面缺陷增加造成穿隧氧化層退 化所導致的情形。

圖 14. 一氧化氮退火法室温資料保存特性。

圖 15. 一氧化氮退火法 10 萬次重複讀寫後室溫資 料保存特性。

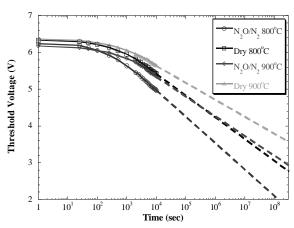

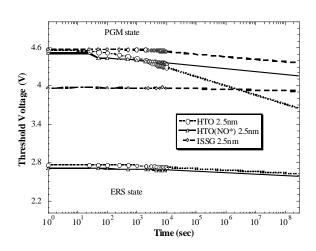

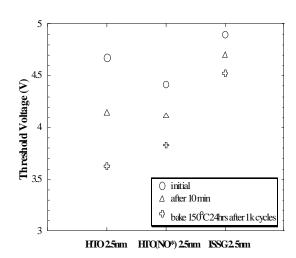

爲了確認一氧化氮退火製程的功效,我們更設計了烘烤實驗,首先觀察經過 1000 次讀寫操作之後,立即在 150°C 之下烘烤 24 小時,結果如圖 16 所示,其中 ISSG 因不易抹除的因素,其電荷流失量相對較少故不列入比較,而 HTO(NO\*)直接穿隧流失的電荷量比 HTO少,顯示介面缺陷上由於氮原子的填入發揮了作用,提高資料的耐久性與保存性;其次更進一步的將 HTO(NO\*)試片執行在 150°C 之下持續烘烤 7 天的嚴格測試條件,如圖 17 所示,外插至 10 年後 HTO(NO\*)仍然具有 0.8 V 的操作窗口,滿足業界設計產品的需求。

圖 16. 一氧化氮退火法試片 1 千次重複讀寫後 150 ℃烘烤 24 小時資料保存特性。

圖 17. 一氧化氮退火法 HTO(NO\*) 1 千次重複讀 寫後 150℃烘烤 7 天資料保存特性。

#### 五、結論

本文已成功將兩種不同的穿隧氧化層氮 化技術運用在 SONOS 快閃記憶體的製程上, 並量測其漏電流、寫入/抹除特性及可靠度等 性能。此方法可藉由高溫以及氮原子填補介面 的矽懸鍵等方式,使得穿隧氧化層品質獲得改 進,同時可提升 SONOS 快閃記憶體元件漏電 流特性、耐電荷重複抹/寫進出與電荷保存能 力。

其次更進一步使用一氧化氮退火法,先以沉積方式成長氧化層,再以較短的時間內高溫退火並通入一氧化氮氣體,結果發現 SONOS快閃記憶體元件在漏電流特性、耐電荷重複讀寫與電荷保存等能力皆獲得提升,顯示大部份氮原子可經由擴散進入而堆積在介面上,達到穿隧氧化層氮化技術預期的效果,同時也因為容易掌握成長厚度以及製程時間短而節省熱成本(thermal budget)等優點,因此建議 HTO

成長穿隧氧化層再配合一氧化氮退火法是一種相當好的選擇。故藉由穿隧氧化層氮化技術,可以提升快閃記憶體的元件特性,加速 SONOS 記憶元件未來朝向高容量、低操作電壓之趨勢發展,並可提供後續元件設計與製程實驗之參考運用。

### 誌謝

感謝國家實驗研究院奈米元件實驗室提 供半導體製程設備,以及力晶半導體股份有限 公司等相關技術支援,使本研究得以順利完 成。

# 参考文獻

- [1] Cappelletti P., Golla C., Olivo P., and Zanoni E., <u>FLASH Memories</u>, Kluwer Academic Publishers, pp. 361-364, 2000.

- [2] Masuoka F., Asano M., Iwahashi H., Komuro T., and Tana S., "A New Flash E<sup>2</sup>PROM Cell Using Triple Polysilicon Technology," IEDM Tech. Dig., pp. 464-467, 1984.

- [3] White M. H., Adams D. A., and Bu J., "On the go with SONOS" IEEE Circuits Devices Mag., Vol. 16, No. 4, pp. 22-31, 2000.

- [4] Nasyrov K. A., Gritsenko V. A., Kim M. K., Chae H. S., Ryu W. I., Sok J. H., Lee J. –W., and Kim B. M., "Charge Transport Mechanism in Metal-Nitride-Oxide-Silicon Structures," IEEE Electron Device Letters, Vol. 23, No. 6, pp. 336-338, 2002.

- [5] Joshi A. B., Yoon G., Kim J., Lo G. Q., Kwong D. L., "High-field breakdown in thin oxides grown in  $N_2O$  ambient," IEEE Trans. on Electron Devices, Vol. 40, pp. 1437-1445, 1993.

- [6] Sharma U., Moazzami R., Tobin P., Okada Y., Cheng S. K., Yeargain J., "Vertically scaled, high reliability EEPROM devices with ultra-thin oxynitride films prepared by RTP in N<sub>2</sub>O/O<sub>2</sub> ambient," in IEDM Tech. Dig. pp. 461-464, 1992.

- [7] Lu H. C., Gusev E. P., Gustafsson T., Garfunkei E., Green M. L., Brasen D., and Feldman L. C., "High Resolution Ion Scattering Study of Silicon Oxynitridation," Applied Physics Letters, Vol. 69, No. 18, pp. 2713-2715, 1996.

- [8] Okada, Y., Tobin, P. J., Lakhotia, V., Feil, W. A., Ajuria, S. A., and Hegde, R. I., "Relationship Between Growth Condition, Nitrogen Profile, and Charge to Breakdown of Gate Oxynitrides Grown from Pure N<sub>2</sub>O," Applied Physics Letters, Vol. 63, No. 2, pp. 194-196, 1994.

- [9] Pan, T. M., Lei, T. F., and Chao, T. S., "Robust Ultrathin Oxynitride Dielectrics by NH<sub>3</sub> Nitridation and N<sub>2</sub>O RTA Treatment," IEEE Electron Devices Letters, Vol. 21, No. 8, pp. 378-380, 2000.

- [10] Carr, E. C. and Buhrman, R. A., "Role of Interfacial Nitrogen in Improving Thin Silcon Oxides Grown in N<sub>2</sub>O," Applied Physics Letters, Vol. 63, No. 1, pp. 55-56, July 1993.

- [11] Xu, Z., Lai, P. T., and Ng, W. T., "Enhanced Off-State Leakage Currents in n-Channel MOSFET's with N<sub>2</sub>O-Grown Gate Dielectric," IEEE Electron Device Letters, Vol. 16, No. 10, pp. 436-438, Oct. 1995.

- [12] Chen T. S., Wu K. H., Chung H., and Kao C. H., "Performance improvement of SONOS memory by bandgap engineering of charge-trapping Layer," IEEE Electron Device Letters, Vol. 25, No. 4, pp. 205-207, 2004.

- [13] Fukuda H., Uchiyama A., Kuramochi T., Hayashi T., Iwabuchi T., Ono T., Takayashiki T., "High-performance scaled flash-type EEPROMs with heavily oxynitrided tunnel oxide films," in IEDM Tech. Dig. pp. 465-468, 1992.

- [14] Roy A. and White M. H., "A new approach to study electron and hole charge separation at the semiconductor-insulator interface," IEEE Trans. on Electron Devices, Vol. 37, Issue 6, part 1, pp.1504-1513, 1990.