# 運用六標準差手法改善平面功率元件 的抗靜電放電能力

著者/江惠民 林谷鴻

國立高雄應用科技大學工業工程與管理系研究生

國立高雄應用科技大學工業工程與管理系教授

六標準差手法從1980年代於摩托羅拉開始建立起,至今已經發展成為一套完整的方法論。本研究以平面功率元件為研究對象,探討如何改善其抗靜電放電能力。研究以六標準差改善手法DMAIC為基礎,將國內外相關文獻所提出之研究結果加以整理及篩選,建構出研究方法。並依照六標準差改善步驟,進行平面功率元件之產品與製程結構的流程分析,探討出影響抗靜電放電能力的關鍵因子。最後搭配田口實驗設計,將關鍵因子設定不同水準進行試驗,在滿足反向崩潰耐壓規格要求的前提下,取得最佳參數組合,改善平面功率元件的抗靜電放電能力,並透過驗證與追蹤系統確認該改善效果。就整體研究的結果而言,六標準差手法可成功應用於改善平面功率元件的抗靜電放電能力。

# 壹、前言

# 一、研究背景與動機

平面技術於1960年代開發至今已有50年,其廣泛應用於半導體產品,包含積體電路(IC)與功率元件。相較於處理信號的積體電路,功率元件是處理能量。在功率元件所處理的能量中,靜電放電(ESD)是最難被預測與掌握。隨著消費性電子產品輕、薄、短、小的發展趨勢,各項元件之功能、特性無不被利用到其性能的極限。因此改善產品能力高於競爭對手,就可提升公司的競爭力。在半導體功率元件的產品特性中,以ESD的耐受能力最受矚目。

# 二、研究目的

功率元件之主要功能為整流(Rectify)、穩壓

(Regulate)與保護(Clamping)。在半導體領域中,Discrete功率元件並無像積體電路般的高進入門檻與高附加價值,導致產業界投入資源短少,技術的創新即不如積體電路般的迅速與亮麗。然而它卻被廣泛的使用於各種的電子系統中,一旦Discrete功率元件失效,即會造成整個系統(含有精密積體電路)失效。鑒於如此重要的功率元件甚少被研究,本研究將探討功率元件與抗靜電能力相關之因素,並藉由六標準差手法改善標的產品之抗靜電能力。

# 貳、文獻探討

## 一、六標準差

標準差 (σ; Sigma) 是個古希臘字,在統計領域中它代表變異程度,也就是一個群體資料中之離散程度(林志良,2009)。六標準差在統計學的意義是指

當所觀察的資料呈現正態分佈且平均值無偏離規格中心時,其整體分佈超出正負六個標準差的機率為0.002ppm(Parts Per Million)(張政豪,2009)。蘇朝墩(2009)指出,Motorola公司在發展六標準差管理時,發現產品在實際生產現場由於各種因素例如人員、機台、材料、環境狀況與變異的影響,所展現出來的績效平均會比在實驗室原始設計偏移1.5個標準差。因此,考慮到可能的1.5個標準差製程偏移,符合現實調整所展現出來的失效機率,其六標準差水準為3.4ppm。

在1980年代初期,Motorola可以做到三個標準差,但是日本廠商可達四個標準差以上的品質水準(蘇朝墩, 2009)。1983年,在Motorola發展六標準差的初期,由該公司之信賴性工程師Bill Smith發表的報告指出,在完全無誤的狀況下組裝,最後交到終端客戶手中的產品才有可能不會出錯(蔡忠恕, 2004)。此份報告引發一連串的討論,最後他們認為當規格供差涵蓋六標準差時,才是可靠的產品品質。

六標準差手法是一套完善的改善系統一DMAIC(Define、Measure、Analyze、Improve、Control)流程,也就是「定義、量測、分析、改善、管控」的流程,是藉由環環相扣的作業步驟,以非常完整的數據分析,重新審核工作的流程、步驟、方式等進而改善並持續保存成果。其簡要定義説明如下:

定義(Define):具體描述現況問題,確認關鍵與影響,找出CTQ(Critical to Quality),設定目標與範圍及界定顧客要求。

量測(Measure):運用管理及統計工具,決定要收集的資料與方法並收集資料,驗證問題與流程、衡量作業績效及收集資料。

分析(Analyze):根據抽樣計畫,分析收集數據確認改善目標,確認關鍵流程輸入變數、確認所有變數來源及評估流程設計。

改善(Improve):針對關鍵變數問題,訂定改善方案,設計新流程與測試追蹤改善後的關鍵變數是否壓縮到最小。

管制(Control):對變數量測系統的持續有效管制,建立關鍵變數的流程管制計畫,使流程能持續改善。

## 二、田口品質工程

田口玄一(Genichi Taguchi)先生出生於1924年,1962年取得日本九州大學博士學位,同年第一次取得Deming Award(戴明獎,日本品質界最高榮譽,共獲得四次)。田口先生在任職於日本電話與電報公司的期間,逐漸發展他的品質工程方法。該方法於1980年田口博士訪問美國AT&T(美國電話電報公司)貝爾實驗室,用以執行內部的一些品質改善計畫,成功的試驗結果使西方世界開始接受該方法,並使田口博士舉世聞名,該方法並被美國工業界稱為田口方法(Taguchi Methods)(李輝煌,2009)。自此開始,全世界各地將田口方法用於各種製程改善以及產品改良中,甚至更前面的產品研發設計階段,田口玄一博士可説是"品質是設計出來"主張的代表性人物(蘇朝墩,2009)。

就品質工程而言,田口博士將其區分為線上品管 (On-Line OC)與線外品管(Off-Line OC)。線上品管 包括製程管制、異常的矯正與預防等,SPC或管制圖 的應用為線上品管的一種(徐世輝, 1996)。線外品管 是指產品在未進入生產線生產前的設計階段所進行的 品質管制工作(戴久永, 1996)。田口博士為推廣線外品管,使產品或製程最佳化,因而發展損失函數、信

號雜音比、實驗設計、直交表等工具,並將"設計 品質"的積極態度融入其推廣田口方法裏(江季哲, 2008)。

傳統上的做法,對於品質特性多以平均值得概念來量測;蘇朝墩(2009)提到,田口博士是以信號雜音比(Signal-to-Noise Ratio; 簡稱S/N比)來衡量,S/N比越高,代表信號越強、雜音越小,也就是品質越好。反之,S/N比越低,代表信號越弱、雜音越大,也就是品質越差(林志良, 2009)。S/N比的推算,是把損失函數取對數轉換而來,如此更容易計算,用以替代損失函數作為衡量產品績效的準則(江季哲, 2008)

李輝煌(2009)描述田口實驗設計包含系統設計、參數設計與允差設計等三個階段,其中參數設計是田口方法的精華之一,也是最大貢獻的項目。它可使產品或製程對於外來影響的敏感度最低,亦即使產品或製程達到最穩定、最小變異、最小損失(成本最小)的狀況。一般而言,可以依序用縮小變異再調整目標兩階段最佳化程序(two-stage optimization procedure)來達成。穩健參數設計的基本原理是:藉由降低變異原因的影響,而不是去除變異原因,來改善產品品質。

蔡政達(2008)指出,田口博士考量到傳統單因子實驗設計的完整性不佳,與全因子實驗設計規模浩大導致耗費成本與時間,因而發展出直交表(Orthogonal Array)實驗計畫架構,再結合損失函數以及信號/雜音比(S/N比),以經濟、有效的方式進行試驗。雖然田口試直交表仍有些疑慮(亦即兩因子間的效應並非在完全相同的因子組合條件下計算出來的),但其仍是兼顧成本與精確度的很好折衷方法。

## 三、靜電放電

靜電(Static Charge)是靜止的不平衡電荷(詹奕倫, 2005),該電荷可能是由摩擦、傳導或感應的方式使物體(包含人)帶電,其中以摩擦造成人體帶電最常見。摩擦會造成人體帶電的原因是每個物質對電子的施予及接受的程度不同,當兩個原本為電中性(電荷平衡)的物質接近、摩擦時,會造成電子的轉移,使物質分別帶正電與負電。常見而又容易忽略的摩擦如走動時

鞋子和地面摩擦,座椅和地面摩擦,或是坐在椅子上 衣服與椅子摩擦等。

靜電放電是指帶有靜電之物體接觸到其他導體(董順萍,2006),由於兩個物體間的電壓差距,造成的瞬間電荷轉移。以人體所能累積的靜電而言,可以高達數拾KV(仟伏特)。如果被靜電放電的對象為電子產品或零件,若該對象的抗靜電能力不高時,輕則出現暫時失效,嚴重時會造成物理性的永久失效(簡旻助,2001)。

靜電放電所涉及的範圍極廣,目前工業界依照其影響方式規範出幾種放電模式(陳忠仁, 2004):

人體放電模式(Human-Body Model, HBM):模擬當人體因各種因素累積電荷,再藉由手指接觸對零件放電的模式。此放電的過程會在短短數百納秒(ns)的時間內產生數安培的瞬間放電電流,進而對零件造成毀損。對一般可耐受HBM 2Kv的零件來說,在2~10 ns時間內,瞬間的電流峰值可達1.33A。

機器放電模式(Machine Model, MM): 1970年代由日本人根據HBM的最嚴重狀況所發展出來,其模擬機器設備(例如測試夾具、機器手臂…等)累積靜電荷之後,再接觸到零件並對其放電。由於機器設備的等效電容大於人體,所以可以儲存更多的電荷;更因為機器多為金屬,所以接觸阻抗低,因而放電的速度快,因此MM與HBM的差異在於其對零件所造成的毀損更大(數拾納秒內產生數安培電流)。

元件充電模式(Charged-Device Model, CDM):指元件因各種因素而在內部累積了靜電荷,雖然在慢慢累積電荷的過程元件並未被損傷,然而當此帶有靜電荷的元件在製程過程中接觸到接地導體時,元件內部的靜電荷即會由接腳瞬間流出而形成放電現象並造成元件的損壞。此種模式的放電時間更短,約只有幾個納秒,且因每個元件的差異而更難真實模擬。

電場感應模式(Field-Induced Model, FIM):指當元件因輸送過程或其他因素經過某一電場時,其相對極性的電荷會因為電場而轉移排出,如此等同累積了靜電荷,這些靜電荷會以類似CDM放電出來(陳明武,2005)。

5

從上述資訊得知,FIM與CDM類似,但不容易真實模 擬。MM源自於HBM,而人體是最常見的靜電來源,因此 本研究採HBM為主要衡量方式。表1整理了各種放電模 式的規格等級,若元件宣稱具備抗靜電能力,以HBM而 言需能夠通過至少2kV的ESD測試。

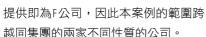

在本案例中,W公司陸續接受到來自市場的客戶回饋 如圖1,反應某功率元件產品有電性功能的規格缺陷。 依據資訊顯示,除了於部分客戶的零件驗證階段出現 與競爭對手在抗靜電能力有明顯差異,亦於其他客戶 的生產線以及最終客戶端出現組裝好的系統成品有品 質異常現象,造成W公司被迫退出某些市場,以及公司 商譽受損。

## 參、研究方法與實例驗證

## 一、研究方法

本研究依照DMAIC各階段,規劃其 所展開的內容以及其可使用的方法如 表2所示:

# 二、定義階段

在本研究中,個案公司是屬於一 家半導體功率元件的封裝測試公司 (以下簡稱W公司),其主要業務是作 功率元件的封裝測試再銷售給3C產品 的製造工廠。該公司的晶片來源,有 八成是來自是同集團的晶片擴散公司 (以下簡稱F公司)。本案例所探討的 產品為一成熟的功率元件,其晶片的

提供即為F公司,因此本案例的範圍跨 圖1功率元件之問題件數趨勢圖(資料來源:本研究整理)

#### 表1 各種放電模式的規格等級(資料來源:本研究整理)

| 依據    | ESDA-STM5.1-2001 | ESDA-STM5. 2-1999 | ESDA-STM5.3.1-1999 |

|-------|------------------|-------------------|--------------------|

| Class | НВМ              | MM                | CDM                |

| 1     | 0 ~ 1.999 Kv     | <100 V            | <125 V             |

| 2     | 2 ~ 3.999 Kv     | 100 ~ 199 V       | 125 ~ 249 V        |

| 3     | 4 ~ 15.999 kV    | 200 ~ 399 V       | 250 ~ 499 V        |

| 4     |                  | ≥400 V            | 500 ~ 999 V        |

| 5     |                  |                   | 1 kV ~ 1.499 kV    |

| 6     |                  |                   | 1.5 kV ~ 1.999 kV  |

| 7     |                  |                   | ≥2 kV              |

#### 表2 DMAIC各階段內容展開表(資料來源:本研究整理)

| Stage        | 內容                                              | 使用方法                          |

|--------------|-------------------------------------------------|-------------------------------|

| 定義<br>Define | 1. 定義問題<br>2. 確認關鍵特性(CTQ/CTC)-Y<br>3. 設定專案範圍與目標 | 5W1H、柏拉圖<br>QFD<br>SIPOC      |

| 量測Measure    | 1. 決定要收集的數據與方法<br>2. 收集數據                       | 儀器校驗、MSA                      |

| 分析Analyze    | 1. 探討產品特性, 分析Y的變異來源<br>2. 找出影響特性Y的關鍵因子X         | 流程分析、5M1E、魚骨圖、關連圖、失<br>效樹、柏拉圖 |

| 改善Improve    | 1. 找出最佳關鍵因子組合<br>2. 驗證最佳關鍵因子組合的有效性              | 相關分析、田口實驗設計法、統計檢定<br>方法       |

| 控制Control    | 1. 更新管控系統<br>2. 追蹤改善後的關鍵特性-Y                    | 愚巧法<br>柏拉圖、管制圖                |

#### 表3 HBM ESD測試結果-W公司(資料來源:本研究整理)

|     | ±1 kV | ±2 kV | ±3 kV | ±4 kV | ±5 kV | ±6 kV | ±7 kV | ±8 kV |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| W公司 | 0/5   | 2/5   | 3/3   | _     | _     | _     | _     | _     |

| V公司 | 0/5   | 0/5   | 0/5   | 0/5   | 0/5   | 1/5   | 4/4   | _     |

#### 表4 HBM ESD測試結果-H公司(資料來源:本研究整理)

|     | ±1 kV | ±2 kV | ±3 Kv | ±4 kV | ±5 kV | ±6 kV | ±7 kV | ±8 kV |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| W公司 | 0/5   | 1/5   | 4/4   | _     | _     | -     | _     |       |

| V公司 | 0/5   | 0/5   | 0/5   | 0/5   | 0/5   | 2/5   | 3/3   | 1     |

基於問題的嚴重性與影響範圍廣大,改善專案小組立即被組織起來,目標產品為此平面功率元件。依據研究方法所提及的步驟,問題被定義為平面功率元件的抗ESD能力不足,其亦為此案例的關鍵品質特性,專案目標為改善此次產品抗ESD能力不足的問題到滿足顧客需求,甚至超越競爭對手。專案範圍是從晶片端的改善到封裝好產品的功能提升,並通過客戶零件認證與應用的功能需求。

## 三、量測階段

由於關鍵品質特性Y是平面晶片之功率元件的抗ESD能力,根據文獻探討的結論,決定以符合MIL-STD-883E Method 3015.7規範的ESD測試機台做HBM的數據收集。在決定好測試機台之後,繼續執行收集數據。由於ESD測試為破壞性測試,為避免測試失誤,因此同時間準備一組樣品送外部實驗室H公司測試,再將測試結果作對比。測試的結果如下表3與4:

### 四、分析階段

從測試結果看來,兩家測試系統(W公司與H公司)的 測試結果差異不大;W公司的元件都只能通過±1 kV, 在±2 kV時就會出現不良,而在±3 kV時全部失效。 至於V公司的元件都能通過±5 kV,在±6 kV時就會出 現不良,而在±7 kV時全部失效。從上述的測試結果 得知,W公司的功率元件無法通過HBM的Class 1等級 2kV,而V公司則可以通過Class 3等級4kV。

面對產品能力有此明顯的差異,在W公司內部要追查出影響品質特性Y的因子X,最簡單的方式就是以5M1E的方法展開調查。通常當功率元件有明顯的Y差異,就封測的角度而言,首先調查的是材料(晶片)的抗靜電能力。於是,經過隨機抽樣的三組晶片被投入封裝試驗,完成封裝之後再重新執行ESD測試,測試結果類似表4量測階段的結論,都無法通過Class 1等級2kV,於是在W公司可以將Y的關鍵變異因子X定義為晶片抗ESD

表5 製程控制因子水準表(資料來源:本研究整理)

| 代號 | 因子                 | 因子 説明                          |    | 水準2 | 水準3 |

|----|--------------------|--------------------------------|----|-----|-----|

| A  | 厚度    磊晶層的厚度,單位為um |                                | A1 | A2  |     |

| В  | 阻值                 | 磊晶層的阻值,單位為Ω-cm                 |    | B2  | В3  |

| С  | Dose量              | Dose量,單位為原子數                   | C1 | C2  | C3  |

| D  | Drive In Temp      | ive In Temp Drive In Temp,單位為℃ |    | D2  | D3  |

| Е  | Drive In Time      | Drive In Time,單位為分鐘            | E1 | E2  | Е3  |

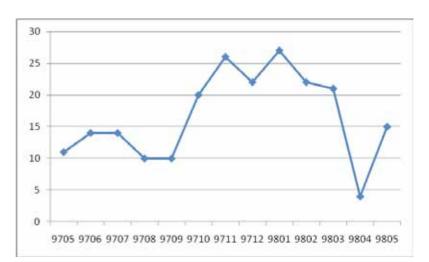

圖2 功率元件結構與運作概念圖

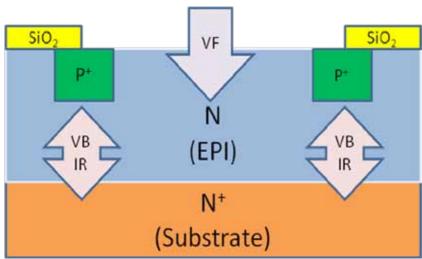

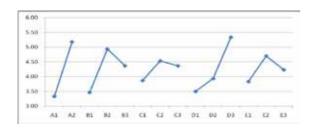

圖3 S/N比的因子反應圖(資料來源:本研究整理)

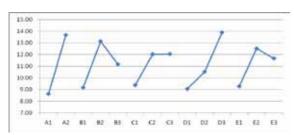

圖4 品質特性的因子反應圖(資料來源:本研究整理)

能力不足。然而從實際狀況來看,此樣的結論無法對現實狀況有任何的幫助,因此必須繼續推動F公司的晶片改善。

首先必須探討晶片製程中會影響品質特性Y的各項可能性,而達到的方式則是從晶片的運作原理與製作流程探討起。平面功率元件的製造過程需先於原晶片上長一層磊晶層,再於該磊晶層上擴散入P+層,整個過程與傳統型結構的主要差異在於磊晶層的應用,唯有穩定的磊晶層才能使平面功率元件達到高品質的目標。磊晶層長成後的主要特性為阻值與厚度,通常厚度越厚、阻值越大的EPI層可以做成較高的耐崩潰電壓(Breakdown Voltage, VB)產品。

圖4.8 簡介某種功率元件的結構,在N+的基座 (Substrate)上長一層N型磊晶層,再採用可形成正電荷的硼(Boron)材料於該磊晶層上固定位置摻雜擴散入為P+層。從該圖可得知,功率元件的運作概念為,正

#### 表6 實驗的平均值、標準差及S/N比紀錄表(資料來源:本研究整理)

| Exp | A | В | С | D | Е | VB平均值  | P1 | P2 | Р3 | P4 | P5 | ESD平均值 | ESD標準差 | S/NH  |

|-----|---|---|---|---|---|--------|----|----|----|----|----|--------|--------|-------|

| 1   | 1 | 1 | 1 | 1 | 1 | 138. 4 | 1  | 1  | 2  | 1  | 1  | 1.2    | 0.4    | 0.7   |

| 2   | 1 | 1 | 2 | 2 | 2 | 155. 6 | 2  | 4  | 5  | 3  | 4  | 3. 6   | 1. 1   | 9.8   |

| 3   | 1 | 1 | 3 | 3 | 3 | 147. 4 | 2  | 3  | 5  | 4  | 3  | 3. 4   | 1. 1   | 9. 4  |

| 4   | 1 | 2 | 1 | 1 | 2 | 146.0  | 2  | 4  | 2  | 3  | 4  | 3. 0   | 1.0    | 8. 3  |

| 5   | 1 | 2 | 2 | 2 | 3 | 166. 2 | 3  | 3  | 5  | 4  | 6  | 4. 2   | 1.3    | 11.5  |

| 6   | 1 | 2 | 3 | 3 | 1 | 161.0  | 6  | 5  | 6  | 5  | 6  | 5. 6   | 0. 5   | 14. 9 |

| 7   | 1 | 3 | 1 | 2 | 1 | 156.8  | 1  | 3  | 2  | 1  | 3  | 2. 0   | 1.0    | 3. 1  |

| 8   | 1 | 3 | 2 | 3 | 2 | 162. 0 | 4  | 3  | 4  | 5  | 5  | 4. 2   | 0.8    | 12.0  |

| 9   | 1 | 3 | 3 | 1 | 3 | 147.0  | 2  | 3  | 2  | 3  | 4  | 2.8    | 0.8    | 8. 0  |

| 10  | 2 | 1 | 1 | 3 | 3 | 157.0  | 5  | 5  | 5  | 4  | 5  | 4.8    | 0.4    | 13.5  |

| 11  | 2 | 1 | 2 | 1 | 1 | 149. 2 | 2  | 4  | 5  | 3  | 2  | 3. 2   | 1.3    | 8. 5  |

| 12  | 2 | 1 | 3 | 2 | 2 | 167. 6 | 4  | 5  | 4  | 5  | 5  | 4. 6   | 0.5    | 13. 1 |

| 13  | 2 | 2 | 1 | 2 | 3 | 166.0  | 5  | 4  | 5  | 4  | 6  | 4.8    | 0.8    | 13. 3 |

| 14  | 2 | 2 | 2 | 3 | 1 | 167.0  | 6  | 6  | 6  | 8  | 7  | 6. 6   | 0. 9   | 16. 2 |

| 15  | 2 | 2 | 3 | 1 | 2 | 161.8  | 5  | 6  | 5  | 5  | 6  | 5. 4   | 0.5    | 14. 5 |

| 16  | 2 | 3 | 1 | 3 | 2 | 174. 2 | 8  | 7  | 8  | 7  | 7  | 7. 4   | 0.5    | 17. 3 |

| 17  | 2 | 3 | 2 | 1 | 3 | 169. 2 | 5  | 6  | 7  | 5  | 4  | 5. 4   | 1.1    | 14. 2 |

| 18  | 2 | 3 | 3 | 2 | 1 | 154. 8 | 5  | 3  | 5  | 5  | 4  | 4. 4   | 0. 9   | 12.3  |

AVE 11.15

#### 表7 S/N比的因子反應表(資料來源:本研究整理)

|             | A      | В      | С      | D      | Е      |

|-------------|--------|--------|--------|--------|--------|

| Level 1     | 8. 63  | 9. 16  | 9. 38  | 9.04   | 9. 27  |

| Level 2     | 13. 66 | 13. 13 | 12. 03 | 10. 51 | 12. 51 |

| Level 3     |        | 11. 15 | 12.04  | 13.89  | 11.66  |

| Range       | 5. 03  | 3. 97  | 2. 67  | 4. 84  | 3. 24  |

| Rank        | 1      | 3      | 5      | 2      | 4      |

| Significant | Yes    | Yes    | No     | Yes    | No     |

向特性以元件中心為作用區,由上往下通往N+層,其所產生的品質特性值為順向壓降VF;而反向特性來自於環繞在晶粒邊緣的P+層,亦即保護環(Guard Ring)的電場展開,當展開範圍越廣的材料,其耐崩潰電壓VB值越高,此時其抗ESD的能力也越高,其所產生的品質特性值為反向耐崩潰電壓VB與漏電流IR(Leakage Current)。

從上述功率元件的產品結構探討與製造流程分析得知,要改善功率元件的抗靜電能力,必須從控制其保護環的驅入深度(Xj)著手,而影響驅入深度的參數為Dose量與驅入條件(温度與時間)。基於磊晶層厚度與摻雜擴散的可達深度有關連,其會影響可驅入深度,進而影響反向耐崩潰電壓VB,同時磊晶層的阻值亦會影響順向壓降VF,所以磊晶層的選擇亦需列入首要考量。

# 五、改善階段

經由上一階段的分析與探討得知,影響功率元件抗 靜電能力的關鍵因子分別是磊晶層的厚度、磊晶層的 阻值、離子植入的Dose量、Drive In温度與Drive In 時間。本階段採用田口實驗計畫法,將上述的五個關鍵因子設定各種不同的水準進行試驗,目標在可以滿足反向崩潰耐壓規格要求的前提下,改善產品耐靜電放電的能力。當取得最佳參數組合,再以田口方法預測改善效果,並實際導入試驗,比較最佳參數的有效性。

首先依照田口方法的步驟,針對製程控制因子進行調查,以了解在系統中各因子的可能水準,再以之建立製程控制因子水準表如表5。

由於變動因子有五個,且有一個是2個水準,假設所有因子間無交互作用,因此採用田口L18直交表。表6是根據L18直交表執行了18組試驗的結果,其每組先量測取得VB的平均值,再測量5組ESD能力的數據,最後經由計算得知ESD平均值、標準差與S/N比。其中S/N比所採用的公式如下式,而S是標準差,n是測試數量。

$$S/N = -10\log(\frac{1}{n}\sum_{i=1}^{n}\frac{1}{v_i^2})$$

表8 品質特性的因子反應表(資料來源:本研究整理)

|             | A     | В     | С     | D     | Е     |

|-------------|-------|-------|-------|-------|-------|

| Level 1     | 3. 33 | 3. 47 | 3. 87 | 3. 50 | 3. 83 |

| Level 2     | 5. 18 | 4. 93 | 4. 53 | 3. 93 | 4.70  |

| Level 3     |       | 4. 37 | 4. 37 | 5. 33 | 4. 23 |

| Range       | 1.84  | 1.47  | 0.67  | 1.83  | 0.87  |

| Rank        | 1     | 3     | 5     | 2     | 4     |

| Significant | Yes   | Yes   | No    | Yes   | No    |

實驗接下來是針對試驗結果進行因子效應分析。所謂因子效應,是指製程控制因子的水準變動,對於S/N比或品質特性影響的程度。亦即例如當因子A由水準A1變動到A2時,S/N比或品質特性的平均變動量。藉由因子效應分析,我們可以得到對S/N比及品質特性的重要影響參數;同時依據本案例S/N比越大越好的概念加上品質特性望大、望小、望目的特性取得各因子的最佳參數水準。首先算出S/N比的因子反應表如表7與因子反應圖如圖3所示。由上列因子反應表7的Rank列可得知,對S/N比的影響程度依序分別是ADBEC,亦即依序是EPI厚度、DriveIn 問題及Dose量。接下來依照一半準則取一半的因子為重要因子,因此A、D、B三個因子即為對S/N比的重要影響參數。

前面的分析是針對S/N比的影響,亦即因子水準間變動對品質特性變異的影響,以此可以決定降低品質特性變異的控制因子與其所對應的最適當水準。然而,從文獻探討可得知,最佳化參數設計的程序是先縮小變異,再調整品質特性使其符合品質目標。因此需再算出品質特性的因子反應表如表8與因子反應圖如圖4:

由上列因子反應表3.7的Rank列可得知,對品質特性的影響程度依序分別是A D B E C,亦即依序是EPI厚度、Drive In温度、EPI阻值、Drive In時間及Dose量。依照一半準則取一半的因子為重要因子,因此A、D、B三個因子即為對品質特性的重要影響參數。

從因子效應的數據分析結果得知,對S/N比的重要影響參數與對品質特性的重要影響參數皆為A、D、B三個因子,因此只要對A、D、B三個因子的水準進行調整,即可達到縮小變異與調整品質特性到符合品質目標的效果。再利用因子反應表與因子反應圖,可以取得最

佳參數水準組合,如此即可有效完成改善。從因子反應表7與因子反應圖3的結果得知,對S/N比而言,最佳的參數水準組合為:A2 B2 C3 D3 E2。再從因子反應表8與因子反應圖4的結果得知,對品質特性而言,最佳的參數水準組合為:A2 B2 C2 D3 E2。考量到C控制因子在因子反應表7與因子反應圖3中,C2與C3水準的效應差距不大,對比其在因子反應表8與因子反應圖4的效應表現有明顯的差距,因此針對C控制因子的水準決定選擇為C2。於是實驗最後的最佳製程因子水準組合是:A2 B2 C2 D3 E2。

由於本研究初始假設各因子間無交互作用狀況,因此可參考表6、7與8用加法模式估算、預測新舊參數組合的效果。首先估算原始參數水準組合(A1B3C1D2E1)的S/N比是11.15+(8.63-11.15)+(11.15-11.15)+(9.38-11.15)+(10.51-11.15)+(9.27-11.15)=4.35,利用相同的方法可估算出原始的品質特性為2.3。再依照新的參數水準組合(A2B2C2D3E2)預測改善後的S/N比為20.63,而品質特性為7.7。從上述估算、預測結果可得知改善效果為:S/N比由4.35 20.63,品質特性由2.3 7.7。就數字的觀察而言,此改善效果可謂顯著且成功;然而,最後且有效的結論仍需以實際試行的結果來判定,因此決定以新參數組合投入試驗,表9整理出新舊製程參數組合的試驗結果。

從表9的結果可得知,採用新參數組合可得到改善效果為: S/N比從3.06提升為17.94,品質特性從2.0改善為7.9,此結果與田口方法所預測的結果接近,在S/N比的差異,推算應為機台測試刻度與已達測試極限所造成的結果。茲整理估算預測與實際試驗的改善前後S/N比與品質特性於下表10,從該表可明顯觀察出改善的效果差異。

表9 新舊製程參數組合試驗結果紀錄表(資料來源:本研究整理)

| EXP                 | P1  | P2 | Р3 | P4 | P5 | ESD平均值 | ESD標準差 | S/NH   | VB平均值  |

|---------------------|-----|----|----|----|----|--------|--------|--------|--------|

| 原參數組合<br>A1B3C1D2E1 | 1   | 3  | 2  | 1  | 3  | 2      | 1.00   | 3. 06  | 156.8  |

| 新參數組合<br>A2B2C2D3E2 | 7.5 | 8  | 8  | 8  | 8  | 7. 9   | 0. 22  | 17. 94 | 175. 2 |

表10 估算預測與實際試驗的改善前後S/N比與品質特性整理表 (資料來源:本研究整理)

|      | S/1   | N比     | 平均值  |      |  |  |

|------|-------|--------|------|------|--|--|

|      | 原參數   | 新參數    | 原參數  | 新參數  |  |  |

| 估算預測 | 4. 35 | 20. 63 | 2. 3 | 7. 7 |  |  |

| 實際試驗 | 3.06  | 17. 94 | 2    | 7. 9 |  |  |

將新舊製程參數組合的試驗結果以統計檢定的方式 確認其顯著性,從t檢定的檢定結果可得知,在95%的 信心水準下,新舊參數組合所呈現出來的試驗結果是 顯著不同(P value=0.000209852),亦即改善結果是有 明顯的差異。

## 六、控制階段

為確保所有生產環節都依照新參數組合執行產品的生產,更新管控系統的部分依照材料供應流程區分為幾個步驟:在F公司的部分有內部PCN 變更通知以及外部ECN通知、材料規格清單變更、製程參數調整、生產Traveler sheet或Bar Code系統改版;在W公司的部分有內部PCN通知以及外部ECN通知、材料規格清單變更、生產Traveler sheet或Bar Code系統改版。

本研究案例的改善動作自9807區間開始導入,雖然W公司於9804區間採取臨時措施與被迫暫時退出某些市場的處置使狀況瞬間舒緩;然而由於功率元件的產業特性:問題會集中於出貨後一季到半年間反應到高峰值,之後才會逐月下降反應件數,並且呈現一個長尾的分布,平均需費時二至三年才能在問題的反應完全消失。因此問題直到到9808區間才逐漸舒緩,並於9901開始呈現下降的趨勢。鑒於產業的特性,雖然狀況無法立即排除,然而從趨勢的監控可以得知,改良品的導入是明顯有效的。

# 肆、研究結論與未來方向

長久以來,在問題分析與解決的領域中,存在 著各種不同的處理模式與方法論;相較於單一案件 或小規模專案,本研究涉及跨越集團內部公司範圍 的案例,因採用六標準差方法而有明確的成果。六 標準差強調滿足顧客需求與針對事實管理,因此 從SIPOC(Supplier、Input、Process、Output、 Customer)的物流過程中,拆解輸入(Input)增值活 動(Process)輸出(Output)的相互關係,作流程分析 以尋找改善變異、提升品質的契機。本論文探討了相 關文獻之後,採用六標準差解決問題的手法,依照其 DMAIC思維流程,發展出對應步驟的研究方法,再以個 案公司的案例,實際逐步運作定義、量測、分析、改 善進而控制問題,直到問題被追蹤出有效改善。改善 結果為使平面功率元件的抗ESD能力由原本2kV提升到 8kV,超越業界最高等級4kV,成功達到專案目標。除 了於內部測試確定提升ESD能力之外,更於客戶端實際 使用下的問題反應數量呈現下降的趨勢。從整體研究 的結果而言,六標準差手法可成功應用於改善平面功 率元件的抗靜電放電能力。

本研究於改善階段的實驗設計是假設各關鍵因子間無交互作用,在該前提下設計試驗,亦即本案例是屬於單一品質特性的狀況。未來在解決問題的模式架構方面,可嘗試以相同的模式處理多重品質特性的狀況。另外,後續可針對已經探討得到的產品知識,持續探索、精進瞭解該產品的理論架構與操作原理,朝著改善產品的其他能力例如功率損耗的節能領域,或是高電壓能力等應用領域的產品改善前進。

# 參考文獻

- 1 戴久永,1996,品質管理,三民書局,台北。

- 2 徐世輝,1996,品質管理,三民書局,台北。

- 3 簡旻助・2001・深次微米及高頻CMOS的ESD保護電路之研究・清華大學・碩士論文。

- 4 蔡忠恕,2004,「DMAIC」安全文化管理模式應用在高科技產業實例, 成功大學,碩士論文。

- 5 陳忠仁,2004,半導體封裝晶圓抗靜電破壞能力分級之研究,高雄第 一科技大學,碩士論文。

- 6 詹奕倫·2005,高速數位系統中靜電放電保護元件之研究,中山大學,碩士論文。

- 7 董順萍,2006,手持式影像裝置開關線路之靜電防護,交通大學,碩 士論文。

- 8 蔡政達,2008,晶片與玻璃基板接合製程參數最佳化之研究,高雄第 一科技大學,碩士論文。

- 9 江季哲·2008·模糊田口法於多重品質特性製程上之研究-以液晶顯示器製程為例·高雄大學,碩士論文。

- 10蘇朝墩,2009,六標準差,前程文化,台北。

- 11 林志良,2009,晶圓切割製程的穩健設計-六標準差與田口實驗設計的應用,高雄應用科技大學,碩士論文。

- 12 張政豪,2009,運用六標準差手法改善彩色率光片製程不良率,高雄 應用科技大學,碩士論文。

- 13 李輝煌,2009,田口方法:品質設計的原理與實務,高立圖書有限公司,台北。

- 14 ESDA, 2001, For Electrostatic Discharge Sensitivity Testing - Human Body Model (HBM) Component Level, ESD Association Standard Test Method STM 5 1-2001

- 15 ESDA, 1999, For the Electrostatic Discharge Sensitivity Testing - Machine Model - Component Level, ESD Association Standard Test Method STM 5.2-1999.

- 16 ESDA, 1999, For Electrostatic Discharge Sensitivity Testing - Charged Device Model (CDM) Component Level, ESD Association Standard Test Method STM 5.3.1-1999.

- 17 US Department of Defense, 1996, Method 3015.7 Electrostatic Discharge Sensitivity Classification, Microcircuits Test Method Standard MIL-STD-883E.